Overview

CESyMPA: Critical Embedded Systems on Multiprocessor Architectures:

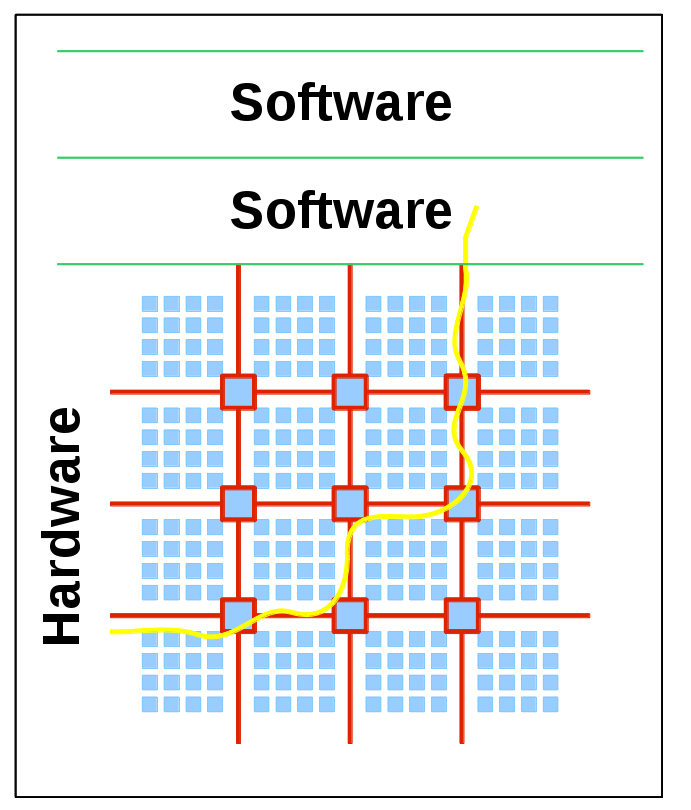

Towards a Certifiable HW/SW Solution

People involved:![]() Florence Maraninchi, VERIMAG (Florence.Maraninchi@imag.fr)

Florence Maraninchi, VERIMAG (Florence.Maraninchi@imag.fr)![]() Pascal Raymond, VERIMAG (Pascal.Raymond@imag.fr)

Pascal Raymond, VERIMAG (Pascal.Raymond@imag.fr)![]() Matthieu Moy, VERIMAG (matthieu.Moy@imag.fr)

Matthieu Moy, VERIMAG (matthieu.Moy@imag.fr)![]() Claire Maiza, VERIMAG (Claire.Maiza@imag.fr)

Claire Maiza, VERIMAG (Claire.Maiza@imag.fr)![]() Stéphane Mancini, TIMA (stephane.mancini@imag.fr)

Stéphane Mancini, TIMA (stephane.mancini@imag.fr)![]() Abbas Sheibanyrad, TIMA (abbas.sheibanyrad@imag.fr)

Abbas Sheibanyrad, TIMA (abbas.sheibanyrad@imag.fr)

The current hardware architectures are not suitable for critical embedded systems, because they are designed for average performance, offering transparent mechanisms at several levels (from the pre-fetching mechanisms in memory controllers to the routing algorithms in networks on a chip, including the very principle of a cache, load balancing techniques, etc.). All these mechanisms are a major obstacle to predictability and determinism, as required by certification authorities. The question of how to design an embedded system for the critical domains, using modern hardware architectures, therefore raises a huge interest, both in companies, and in academia. There is no satisfactory solution yet.

We think that these topics deserve a new and fresh look, “forgetting” about the constraints of existing components or software solutions. In this project, we aim at exploring ways to implement critical systems as software running on multiprocessor architectures, in such a way that the complete solution be simple and provably deterministic, therefore acceptable by certification authorities. We would like to come up with a clear idea of what could be an ideal hardware architecture and design flow for “predictable-by-construction” critical embedded systems. Even if it is not feasible for a number of reasons, ranging from hardware fabrication problems to economic viability, this is scientifically worth trying because it would give an estimation of the distance between such an ideal solution and what exists now, and help identifying the tricky problems with the current hardware.