# Laboratoire VERIMAG

Directeur: Nicolas Halbwachs

Vague A : Campagne d'évaluation 2014–2015

Unité de recherche

Dossier d'évaluation

Unité Mixte de Recherche 5104 CNRS - Grenoble INP - UJF

# Contents

| 1 | Gen | eral Report                                                                                                                                                                                              | 7 |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 1.1 | Introduction                                                                                                                                                                                             | 7 |

|   | 1.2 | Politique scientifique                                                                                                                                                                                   | 7 |

|   | 1.3 | Profil d'activités                                                                                                                                                                                       | 8 |

|   | 1.4 | Organisation et vie de l'unité                                                                                                                                                                           | 9 |

|   |     | 1.4.1 Personnel                                                                                                                                                                                          | 9 |

|   |     | 1.4.2 Gouvernance                                                                                                                                                                                        | 0 |

|   |     | 1.4.3 Services                                                                                                                                                                                           | 0 |

|   |     | 1.4.4 Outils communs                                                                                                                                                                                     | 0 |

|   |     | 1.4.5 Budget, gestion                                                                                                                                                                                    | 1 |

|   |     | 1.4.6 Locaux                                                                                                                                                                                             | 1 |

|   |     | 1.4.7 Animation interne                                                                                                                                                                                  | 1 |

|   | 1.5 | Faits marquants                                                                                                                                                                                          | 1 |

|   | 1.6 | Auto-évaluation                                                                                                                                                                                          | 3 |

|   |     | 1.6.1 Forces                                                                                                                                                                                             | 3 |

|   |     | 1.6.2 Faiblesses $\ldots \ldots \ldots$                                                  | 4 |

|   |     | 1.6.3 Opportunités $\ldots \ldots \ldots$                                                | 4 |

|   |     | 1.6.4 Menaces                                                                                                                                                                                            | 4 |

|   |     |                                                                                                                                                                                                          |   |

| 2 |     | ailed scientific report 1                                                                                                                                                                                |   |

|   | 2.1 | Synchrone Team                                                                                                                                                                                           | - |

|   |     | 2.1.1 Synchrone team: Scientific production                                                                                                                                                              | - |

|   |     | $2.1.1.1  \text{Modeling and simulation}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                               |   |

|   |     | 2.1.1.2 Distributed algorithms $\ldots \ldots \ldots$                                    |   |

|   |     | 2.1.1.3 Decision procedures and abstract interpretation                                                                                                                                                  |   |

|   |     | 2.1.1.4 Automatic testing $\ldots$ 18                                                                                                                                                                    |   |

|   |     | 2.1.1.5 Implementation and analysis $\ldots \ldots \ldots$                               |   |

|   |     | 2.1.2 Synchrone team: Scientific influence                                                                                                                                                               |   |

|   |     | 2.1.2.1 Participation in the spread of the synchronous technology $\ldots \ldots \ldots$ |   |

|   |     | 2.1.2.2 ERC Grant for D. Monniaux $\ldots$ 19                                                                                                                                                            |   |

|   |     | 2.1.2.3 Creation of a startup company: Argosim 19                                                                                                                                                        |   |

|   |     | 2.1.2.4 Long-lasting Collaborations, Industrial Transfer, and Impact on Standards 19                                                                                                                     |   |

|   |     | 2.1.3 Synchrone team: Interaction with the economic, social and cultural environment 20                                                                                                                  |   |

|   |     | 2.1.4 Synchrone team: Internal organization and life of the team                                                                                                                                         |   |

|   |     | 2.1.5 Synchrone team: Training through Research                                                                                                                                                          |   |

|   | 2.2 | DCS Team                                                                                                                                                                                                 |   |

|   |     | 2.2.1 DCS team: Scientific production                                                                                                                                                                    | 1 |

|   |     | 2.2.1.1 System Design                                                                                                                                                                                    | 1 |

|   |     | 2.2.1.1.1 The BIP Design Flow                                                                                                                                                                            | 2 |

|   |     | 2.2.1.1.2 The BIP Framework                                                                                                                                                                              | 2 |

|   |     | 2.2.1.1.3 The Real-Time BIP                                                                                                                                                                              | 3 |

# CONTENTS

|   |     |       | 2.2.1.1.4 Mixed Criticality.                                               | 23 |

|---|-----|-------|----------------------------------------------------------------------------|----|

|   |     |       | 2.2.1.1.5 Distributed Implementation.                                      | 23 |

|   |     |       | 2.2.1.1.6 Performance evaluation.                                          | 23 |

|   |     |       | 2.2.1.2 Security                                                           | 24 |

|   |     |       | 2.2.1.2.1 Proofs of security protocols.                                    | 24 |

|   |     |       | 2.2.1.2.2 Analysis of Security properties                                  | 24 |

|   |     |       | 2.2.1.2.3 Code analysis and vulnerability detection                        |    |

|   |     |       | 2.2.1.3 Software verification and certification                            |    |

|   |     |       | 2.2.1.3.1 Modular techniques for scalar programs.                          |    |

|   |     |       | 2.2.1.3.2 Verification of programs with higher-order data structures.      |    |

|   |     |       | 2.2.1.3.3 Certification of validation tools.                               |    |

|   |     |       | 2.2.1.3.4 Work in collaboration with LIAMA Beijing                         |    |

|   |     |       | 2.2.1.4 Model-based Verification and Synthesis                             |    |

|   |     |       | 2.2.1.1 Model-based technologies                                           |    |

|   |     |       | 2.2.1.4.2 Contract-based and compositional verification                    |    |

|   |     |       | 2.2.1.4.3 Knowledge-based control and distribution                         |    |

|   |     |       | 2.2.1.4.5 Knowledge-based control and distribution                         |    |

|   |     | 2.2.2 | DCS team: Scientific influence                                             |    |

|   |     | 2.2.2 |                                                                            |    |

|   |     |       |                                                                            |    |

|   |     |       | 2.2.2.2 Security                                                           |    |

|   |     | 0.0.9 | 2.2.2.3 Verification technology                                            |    |

|   |     | 2.2.3 | DCS team: Interaction with the economic, social and cultural environment   |    |

|   |     | 2.2.4 | DCS team: Internal organization and life of the team                       |    |

|   | 0.0 | 2.2.5 | DCS team: Training through Research                                        |    |

|   | 2.3 | -     | o Team                                                                     |    |

|   |     | 2.3.1 | Tempo team: Scientific production                                          |    |

|   |     |       | 2.3.1.1 Hybrid Verification by Reachability                                |    |

|   |     |       | 2.3.1.2 Hybrid Verification by Simulation                                  |    |

|   |     |       | 2.3.1.3 Monitoring Temporal Properties                                     |    |

|   |     |       | 2.3.1.4 Conformance Testing of Hybrid Systems                              |    |

|   |     |       | 2.3.1.5 Optimization for Multi-Core Deployment                             |    |

|   |     |       | 2.3.1.6 Other Results                                                      |    |

|   |     | 2.3.2 | Tempo team: Scientific influence                                           |    |

|   |     |       | 2.3.2.1 Hybrid Systems                                                     |    |

|   |     |       | 2.3.2.2 Timed Systems                                                      |    |

|   |     |       | 2.3.2.3 Analog Verification                                                |    |

|   |     |       | 2.3.2.4 Systems Biology                                                    | 34 |

|   |     |       | 2.3.2.5 Verification in General                                            | 34 |

|   |     | 2.3.3 | Tempo team: Interaction with the economic, social and cultural environment | 34 |

|   |     | 2.3.4 | Tempo team: Internal organization and life of the team                     | 35 |

|   |     | 2.3.5 | Tempo team: Training through Research                                      | 35 |

| • | -   |       |                                                                            |    |

| 3 |     | -     | hrough Research                                                            | 37 |

|   | 3.1 |       | s et Habilitations                                                         | 37 |

|   |     | 3.1.1 | Doctorants                                                                 | 37 |

|   |     | 3.1.2 | Séminaires doctorants                                                      | 37 |

|   |     | 3.1.3 | Habilitations                                                              | 37 |

|   | 0.0 | 3.1.4 | Stages de recherche                                                        | 37 |

|   | 3.2 |       | ipation aux formations doctorales et masters recherche                     | 39 |

|   |     | 3.2.1 | Responsabilités à l'Ecole doctorale                                        | 39 |

|   |     | 3.2.2 | Interventions et responsabilités en M2R                                    | 39 |

|   | 3.3 | Organ | isation d'écoles pour doctorants                                           | 39 |

# CONTENTS

| 4            | Per  | spectiv | ves          | 4                                                                                                                            | 41       |

|--------------|------|---------|--------------|------------------------------------------------------------------------------------------------------------------------------|----------|

|              | 4.1  | Summ    | ary of the   | competences                                                                                                                  | 41       |

|              |      |         | on of the d  | lomain for the next five years                                                                                               | 42       |

|              | 4.3  | Organ   | isation of t | the laboratory $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                         | 43       |

|              | 4.4  | Detail  | ed projects  | s of the new teams                                                                                                           | 43       |

|              |      | 4.4.1   | PACSS: 1     | Preuves et Analyses de Code pour la Sûreté et la Sécurité / Proofs and Code                                                  |          |

|              |      |         | Analysis     | for Safety and Security (David Monniaux)                                                                                     | 43       |

|              |      |         | 4.4.1.1      | Safety-critical systems code                                                                                                 | 43       |

|              |      |         | 4.4.1.2      | Non safety-critical industrial applications                                                                                  | 44       |

|              |      |         | 4.4.1.3      | Security code analysis                                                                                                       | 44       |

|              |      | 4.4.2   | Synchron     | e (Matthieu Moy)                                                                                                             | 44       |

|              |      |         | 4.4.2.1      | Virtual prototyping and Simulation                                                                                           | 45       |

|              |      |         | 4.4.2.2      | Distributed Algorithms                                                                                                       | 45       |

|              |      |         | 4.4.2.3      | Implementation and Timing Analysis of Real-Time Embedded Systems                                                             | 46       |

|              |      | 4.4.3   | RSD: Rig     | gorous System Design (Saddek Bensalem)                                                                                       | 46       |

|              |      | 4.4.4   | Tempo (O     | Oded Maler)                                                                                                                  | 48       |

|              |      |         |              |                                                                                                                              |          |

| $\mathbf{A}$ | ppen | dices   |              | 4                                                                                                                            | 49       |

| Δ            | Exe  | cutive  | summary      | v.                                                                                                                           | 51       |

|              | Line | cutive  | Summa,       |                                                                                                                              | /1       |

| B            | Org  | anisati | ion chart    | Ę                                                                                                                            | 55       |

| С            | Inte | ernal r | ules         | Ę                                                                                                                            | 57       |

| Б            | Dec  | oonah i | productio    |                                                                                                                              | 63       |

| D            |      |         |              |                                                                                                                              | ва<br>63 |

|              | D.1  | D.1.1   |              | $\begin{array}{c} \text{on scientifique globale} & \dots & $ |          |

|              |      | D.1.1   |              | Publications                                                                                                                 |          |

|              |      |         |              |                                                                                                                              | 63       |

|              |      | D 1 9   |              |                                                                                                                              | 63       |

|              |      | D.1.2   |              |                                                                                                                              | 63       |

|              |      |         |              | •                                                                                                                            | 63       |

|              |      |         |              |                                                                                                                              | 63       |

|              |      |         |              |                                                                                                                              | 65       |

|              |      |         |              |                                                                                                                              | 65       |

|              |      |         |              | Responsabilités universitaires                                                                                               |          |

|              |      |         |              | Visites de longue durée                                                                                                      |          |

|              |      |         |              | Distinctions                                                                                                                 |          |

|              |      | D.1.3   |              | ons avec l'environnement économique, social et culturel                                                                      |          |

|              | D.2  | -       |              |                                                                                                                              | 67       |

|              | D.2  | D.2.1   |              |                                                                                                                              | 67       |

|              |      | D.2.1   |              |                                                                                                                              | 67       |

|              |      |         |              |                                                                                                                              | 68       |

|              |      |         |              |                                                                                                                              | 74       |

|              |      |         |              |                                                                                                                              | 74       |

|              |      |         |              |                                                                                                                              | 74       |

|              |      | D.2.2   |              | · · · · · · · · · · · · · · · · · · ·                                                                                        | 74       |

|              |      | D.2.2   |              |                                                                                                                              | 75       |

|              |      | D.2.4   |              |                                                                                                                              | 78 78    |

|              | D.3  |         |              |                                                                                                                              | 78       |

|              | 2.0  | D.3.1   |              |                                                                                                                              | 78       |

|              |      | 2.0.1   |              |                                                                                                                              | 78       |

|              |      |         |              |                                                                                                                              | 80       |

|              |      |         |              |                                                                                                                              |          |

3

# CONTENTS

|        |                                                                            | D.3.2<br>D.3.3<br>D.3.4                                                   | D.3.1.3Books, Book Chapters and edited proceedingsD.3.1.4PhD Theses and habilitationsD.3.1.5Other visible publicationsDCS team: SoftwareDCS team: Scientific influenceDCS team: Interaction with the economic, social and cultural environment | 93<br>94<br>94<br>96                                               |

|--------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|        | D.4                                                                        | Tempo                                                                     | $team: production \dots \dots$                                                                                                           |                                                                    |

|        |                                                                            | D.4.1                                                                     | Tempo team: Publications, by Categories                                                                                                                                                                                                        |                                                                    |

|        |                                                                            |                                                                           | D.4.1.1 International Journals                                                                                                                                                                                                                 |                                                                    |

|        |                                                                            |                                                                           | D.4.1.2 International Conferences                                                                                                                                                                                                              |                                                                    |

|        |                                                                            |                                                                           | D.4.1.4 PhD Theses and habilitations                                                                                                                                                                                                           |                                                                    |

|        |                                                                            |                                                                           | D.4.1.5 Other visible publications                                                                                                                                                                                                             |                                                                    |

|        |                                                                            | D.4.2                                                                     | Tempo team: Software                                                                                                                                                                                                                           |                                                                    |

|        |                                                                            | D.4.3                                                                     | Tempo team: Scientific influence                                                                                                                                                                                                               |                                                                    |

|        |                                                                            | D.4.4                                                                     | Tempo team: Interaction with the economic, social and cultural environment                                                                                                                                                                     | 105                                                                |

|        |                                                                            |                                                                           |                                                                                                                                                                                                                                                |                                                                    |

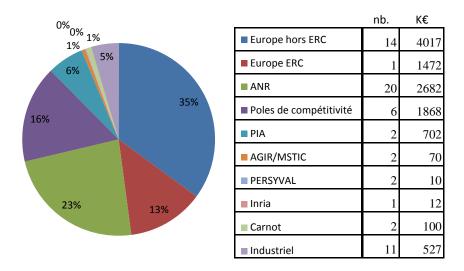

| Е      | List                                                                       | of gra                                                                    | nts                                                                                                                                                                                                                                            | 107                                                                |

| E<br>F |                                                                            | -                                                                         | nts<br>ation document                                                                                                                                                                                                                          | 107<br>147                                                         |

| F      | Risl                                                                       | -                                                                         | ation document                                                                                                                                                                                                                                 |                                                                    |

| F      | Risl                                                                       | <b>c evalu</b><br><b>of sta</b><br>Signed                                 | ation document<br>ff<br>List of Permanent Staff                                                                                                                                                                                                | 147<br>151<br>151                                                  |

| F      | Risk<br>List<br>G.1<br>G.2                                                 | <b>of sta</b><br>Signed<br>Teache                                         | ation document<br>ff<br>List of Permanent Staff                                                                                                                                                                                                | <b>147</b><br><b>151</b><br>151<br>154                             |

| F      | <b>Rist</b><br>G.1<br>G.2<br>G.3                                           | c evalu<br>of sta<br>Signed<br>Teache<br>Resear                           | ation document<br>ff<br>List of Permanent Staff                                                                                                                                                                                                | <b>147</b><br><b>151</b><br>151<br>154<br>154                      |

| F      | <b>Rist</b><br>G.1<br>G.2<br>G.3<br>G.4                                    | of sta<br>Signed<br>Teache<br>Resear<br>Engine                            | ation document         ff         List of Permanent Staff         ers-Researchers         chers         chers         eers, Administrative staff                                                                                               | <b>147</b><br><b>151</b><br>151<br>154<br>154<br>155               |

| F      | <b>Rist</b><br>G.1<br>G.2<br>G.3<br>G.4<br>G.5                             | of sta<br>Signed<br>Teache<br>Resear<br>Engine<br>Tempo                   | ation document         ff         List of Permanent Staff         ers-Researchers         chers         cers, Administrative staff         orary engineers, Postdocs                                                                           | <b>147</b><br><b>151</b><br>151<br>154<br>154<br>155<br>155        |

| F      | <b>Risł</b><br>G.1<br>G.2<br>G.3<br>G.4<br>G.5<br>G.6                      | of sta<br>Signed<br>Teache<br>Resear<br>Engine<br>Tempo<br>PhD S          | ation document         ff         List of Permanent Staff         ers-Researchers         chers         chers         ers, Administrative staff         orary engineers, Postdocs         tudents (PhD defended)                               | <b>147</b><br><b>151</b><br>154<br>154<br>155<br>155<br>155        |

| F      | <b>Risł</b><br>G.1<br>G.2<br>G.3<br>G.4<br>G.5<br>G.6                      | of sta<br>Signed<br>Teache<br>Resear<br>Engine<br>Tempo<br>PhD S          | ation document         ff         List of Permanent Staff         ers-Researchers         chers         cers, Administrative staff         orary engineers, Postdocs                                                                           | <b>147</b><br><b>151</b><br>154<br>154<br>155<br>155<br>155        |

| F<br>G | <b>Risł</b><br>G.1<br>G.2<br>G.3<br>G.4<br>G.5<br>G.6<br>G.7               | of sta<br>Signed<br>Teachd<br>Resear<br>Engind<br>Tempo<br>PhD S<br>PhD S | ation document         ff         List of Permanent Staff         ers-Researchers         chers         chers         ers, Administrative staff         orary engineers, Postdocs         tudents (PhD defended)                               | <b>147</b><br><b>151</b><br>154<br>154<br>155<br>155<br>155        |

| F<br>G | <b>Risk</b><br>G.1<br>G.2<br>G.3<br>G.4<br>G.5<br>G.6<br>G.7<br><b>Lab</b> | of sta<br>Signed<br>Teachd<br>Resear<br>Engind<br>Tempo<br>PhD S<br>PhD S | ation document         ff         List of Permanent Staff         ers-Researchers         chers         chers         cers, Administrative staff         orary engineers, Postdocs         tudents (PhD defended)         tudents (ongoing)    | <b>147</b><br><b>151</b><br>154<br>154<br>155<br>155<br>155<br>160 |

# Avant-Propos

Ce document constitue le rapport d'activité du laboratoire Verimag pour la période allant du 1er janvier 2009 au 30 juin 2014, ainsi que les perspectives pour la prochaîne période. Nous avons choisi de rédiger ce rapport en français pour les parties factuelles et administratives, et en anglais pour les parties scientifiques, de nombreux membres du laboratoires n'étant pas francophones.

Note sur les références bibliographiques : La liste complète des publications de la période est donnée dans l'Annexe D, par équipe et par catégorie. Dans le texte, les clés de référence sont constituées d'une lettre pour l'équipe (S=Synchrone, D=DCS, T=Tempo), d'une lettre pour la catégorie (J=Journal, C=Conference, B=Books and Edited Proceedings, P=PhD Thesis, O=Other visible publication) et d'un numéro d'ordre. Les références externes ou hors période sont données en annexe I.

# Foreword

This document is the activity report of Verimag laboratory for the period comprised between January 1st, 2009 and June 30, 2014, together with the perspectives for the next period. It has been decided to write this report in French for the factual and administrative parts, and in English for the scientific chapters, since many members of the laboratory don't read French.

Note on bibliographic references : The complete list of publications for the period is given in Appendix D, sorted by team and category. In the text, publications are references by keys, made of a letter for the team (S=Synchrone, D=DCS, T=Tempo), a letter for the category (J=Journal, C=Conference, B=Books and Edited Proceedings, P=PhD Thesis, O=Other visible publication) and a number. External and previous references are given in Appendix I.

# Chapter 1

# General Report Présentation de l'unité

# 1.1 Introduction

Verimag a été créé en 1993, d'abord comme unité mixte industrielle avec la société Vérilog, puis, à partir de 1997, comme UMR commune au CNRS, à l'Université Joseph Fourier (Grenoble 1), et à Grenoble INP. Verimag a été dirigé par Joseph Sifakis jusqu'en 2006, et par Nicolas Halbwachs depuis lors.

Le domaine général des recherches menées au laboratoire concerne la conception et la validation des systèmes informatiques embarqués, en privilégiant une approche formelle.

A ce jour, les effectifs sont de 41 permanents (23 enseignants-chercheurs, 8 chercheurs, 6 ingénieurs et 4 administratifs), auxquels il faut ajouter une douzaine de post-doctorants et contractuels, et une trentaine de doctorants. Verimag est hébergé dans des locaux de l'Université Joseph Fourier, situés dans deux bâtiments en lisière du domaine universitaire de Saint-Martin d'Hères et Gières.

# 1.2 Politique scientifique

Initialement focalisés sur la programmation synchrone et la vérification par model-checking, les thèmes de recherche du laboratoire se sont largement diversifiés, notamment vers la modélisation et l'analyse des systèmes temporisés et hybrides (discrets-continus), la sécurité informatique, la modélisation des systèmes à la frontière du logiciel et du matériel (systèmes sur puces, réseaux de capteurs), les méthodes d'analyse par interprétation abstraite, la prise en compte de "propriétés non fonctionnelles"<sup>1</sup>, la conception par composants, l'algorithmique distribuée.

Durant toute la période 2009-2014, le laboratoire a été structuré en 3 équipes, dont on trouvera plus loin les rapports détaillés :

- Synchrone : définition et implantation de langages de programmation temps-réel, approches d'implantation dirigées par les modèles, conception par composants, analyse de pire temps d'exécution ; modélisation fidèle et simulation efficace de systèmes numériques (systèmes sur puce, réseaux de capteurs) incluant des propriétés non-fonctionnelles ; applications du model-checking, fondements et applications de l'interprétation abstraite, méthode SMT ; test automatisé ; algorithmique distribuée.

- Distributed Complex Systems (DCS) : Conception de systèmes embarqués basée sur des modèles à composants, en particulier le langage et la chaîne d'outils BIP qui permet un flot de conception rigoureux, de la vérification passant à l'échelle et des méthodes d'implémentation "correctes par construction" Sécurité : preuve de protocoles de sécurité, formalisation et vérification de propriétés de sécurité, analyse de vulnérabilité de code, test de propriétés de sécurité Vérification de logiciel en particulier basé sur

<sup>&</sup>lt;sup>1</sup>faute d'une meilleure expression : il s'agit de propriétés quantitatives concernant le temps d'exécution, l'occupation mémoire, la consommation énergétique, ...

de l'analyse statique et des procédures de décision, outils de preuve — vérification basée sur des modèles, en particulier modèles d'architecture et modèles non-fonctionnels.

• Tempo : Méthodes et outils pour la validation, la vérification et l'instrumentation de systèmes continus et hybrides, application aux systèmes de contrôle embarqués, aux circuits analogiques, et aux systèmes biologiques ; techniques d'optimisation multi-critères appliquées au déploiement d'applications sur plates-formes multi-coeurs.

Cependant, le domaine de recherche général — les systèmes embarqués — et l'approche générale consistant à s'appuyer sur des méthodes formelles, sont largement communs aux 3 équipes. Un autre trait commun est la mise en œuvre d'une synergie entre la recherche fondamentale et les applications : les thèmes de recherche sont largement inspirés des applications — coopérations et études de cas industrielles —, et les solutions proposées sont confrontées aux applications. Enfin, ces solutions sont très souvent implémentées dans des outils logiciels pérennes. Les frontières des équipes sont perméables, et les collaborations inter-équipes sont nombreuses, avec des projets communs et des publications cosignées.

Le laboratoire bénéficie d'un contexte local très favorable, auquel il prend toute sa part.

- Les thématiques de Verimag occupent une position centrale dans celles du LabEx PERSYVAL, créé en 2012, et dédié à la maîtrise de la convergence des mondes physique et numérique. Nous avons largement participé au montage de ce LabEx et à son animation.

- Verimag a pris une part importante à la création du CRI, Centre de Recherche Intégrative, hébergeant des projets collaboratifs. Joseph Sifakis en assure la direction scientifique, et le groupe "BIP" de l'équipe DCS fait partie du CRI depuis sa création en 2010.

- Verimag participe activement à l'Institut Carnot LSI et au pôle de compétitivité Minalogic.

- Nous avons étroitement participé à la préparation du projet de bâtiment PILSI, qui devrait être disponible en 2016 et héberger 3 laboratoires : le LIG, le LJK, et Verimag, ainsi que l'UMS MI<sup>2</sup>S.

Le laboratoire entretient des collaborations formalisées avec la plupart des laboratoires grenoblois du pôle MSTIC (TIMA, TIMC, LIG, LJK, GIPSA, Institut Fourier), notamment dans le cadre du LabEx PERSYVAL.

Les réseaux Artist, Artist2 et Artist-Design, dont Joseph Sifakis était le principal instigateur, ont assuré au laboratoire une excellente visibilité européenne et internationale. Maintenant terminés, ces réseaux se prolongent par l'action EMSIG (Embedded Systems Special Interest Group<sup>2</sup>), à laquelle nous participons (Joseph Sifakis et Nicolas Halbwachs appartiennent au comité de pilotage). La collaboration de longue date de l'équipe Synchrone avec STMicroelectronics permet au laboratoire d'être visible sur des projets liés à la conception de systèmes sur puce, au niveau européen (projet OpenES dans le cadre CATRENE, projet de projet dans le cadre ECSEL).

Au niveau national, nous participons au GDR GPL<sup>3</sup>, et notamment à son groupe "compilation" que nous avons contribué à créer. Nous sommes très présents dans les projets des investissements d'avenir liés aux systèmes embarqués (d'abord "Briques Génériques du Logiciel Embarqué" - BGLE, puis "Logiciel Embarqué et Objets Communicants" - LEOC) avec 2 projets BGLE en cours, un projet "sécurité numérique" et un projet LEOC en cours de négociation. Nous sommes également très impliqués dans des projets ANR, en collaboration avec des partenaires académiques ou industriels.

| Unité/Equipe          | Recherche<br>académique | Interaction avec<br>l'environnement | Appui à la<br>recherche | Formation par<br>la recherche | Total |

|-----------------------|-------------------------|-------------------------------------|-------------------------|-------------------------------|-------|

| Ensemble              | 57%                     | 5%                                  | 15%                     | 23%                           | 100%  |

| dont équipe Synchrone | 51%                     | 6%                                  | 16%                     | 27%                           | 100%  |

| dont équipe DCS       | 57%                     | 3%                                  | 18%                     | 22%                           | 100%  |

| dont équipe Tempo     | 63%                     | 10%                                 | 5%                      | 22%                           | 100%  |

# **1.3** Profil d'activités

On trouvera en annexe D les éléments factuels justifiant ce profil, tant au niveau global du laboratoire qu'à celui de chaque équipe .

<sup>&</sup>lt;sup>2</sup>www.emsig.net/

$<sup>^{3}</sup>$ gdr-gpl.cnrs.fr

#### 1.4. ORGANISATION ET VIE DE L'UNITÉ

|                                      | UJF           | INP        | CNRS               | Total |

|--------------------------------------|---------------|------------|--------------------|-------|

| Chercheurs et enseignants-chercheurs | 10  MC, 4  Pr | 6 MC, 2 Pr | 3 CR, 4 DR, 1 DREm | 30    |

| Administratifs                       | 3             |            | 1                  | 4     |

| Ingénieurs                           | 1 IE          |            | 1 AI, 4 IR         | 6     |

| Contractuels et postdoctorants       |               | 12         |                    | 12    |

| Doctorants                           |               | 31         |                    | 31    |

| Table 1.1 | : Effect | ifs au | 30 j | uin | 2014 |

|-----------|----------|--------|------|-----|------|

|-----------|----------|--------|------|-----|------|

|                                | Synchrone | DCS             | Tempo    |

|--------------------------------|-----------|-----------------|----------|

| Chercheurs                     | 1CR, 2DR  | 1CR, 1DR, 1DREm | 1CR, 1DR |

| Enseignants-chercheurs         | 6MC, 1PR  | 6MC, 5PR        | 1MC      |

| Ingénieurs                     | 1IR       | 2IR             | 1IR      |

| Contractuels et postdoctorants | 5         | 4               | 1        |

| Doctorants                     | 5         | 16              | 9        |

Table 1.2: Effectifs des équipes

|       | UJF              | INP              | CNRS                           |

|-------|------------------|------------------|--------------------------------|

| 2009  |                  |                  | +1 CR                          |

| 2010  |                  | $+1 \mathrm{MC}$ | +1 IR $-1$ IE                  |

| 2011  | $-1 \mathrm{Pr}$ |                  |                                |

| 2012  | -1 IE            |                  | -2  CR - 1  DR + 1  DR + 1  AI |

| 2013  | $-1 { m MC}$     |                  |                                |

| 2014  | +1  IE           |                  |                                |

| Bilan | -2               | +1               | 0                              |

Table 1.3: Mouvements de personnels permanents

# 1.4 Organisation et vie de l'unité

# 1.4.1 Personnel

Les effectifs au 30 juin 2014 sont donnés par la table 1.1, et la répartition par équipe par la table 1.2. La table 1.3 donne les évolutions des effectifs en personnel permanent au cours de la période. Les enseignants-chercheurs relèvent tous de la 27e section du CNU. Par contre, après la division de la section 7 du CoNRS, si la plupart des membres du laboratoire ont opté pour la section 6, certains se sont mieux reconnus dans la section 7. Cette répartition reflète bien la position du domaine de recherche du laboratoire, à la frontière du logiciel, du matériel et du contrôle.

Dans la période considérée, le laboratoire a bénéficié du recrutement d'une chargée de recherche (Barbara Jobstmann) et d'un assistant-ingénieur (Philippe Genin) CNRS et d'une maître de conférence Grenoble INP (Claire Maïza), de l'arrivée en mutation d'un ingénieur de recherche CNRS (Olivier Lebeltel) et d'un ingénieur d'étude UJF (Patrick Fulconis), et de la promotion d'un CR en DR (David Monniaux). La même période a vu le départ en retraite d'un professeur UJF (Pierre-Claude Scholl) et le passage en éméritat d'un directeur de recherche (Joseph Sifakis), le départ en mutation de 2 ingénieurs d'étude (Claude Dutreilly, CNRS, et Jean-Noël Bouvier, UJF), ainsi que le départ en détachement d'une CR CNRS (Barbara Jobstmann) et d'un maître de conférence UJF (Pascal Lafourcade). En conséquence, actuellement, 3 chercheurs<sup>4</sup> CNRS et un enseignant-chercheur sont en détachement.

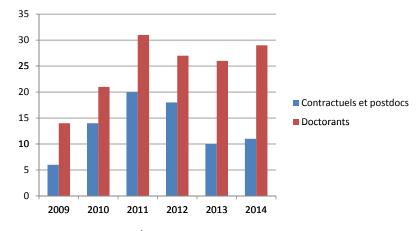

La figure 1.1 donne l'évolution des effectifs non-permanents au cours de la période.

<sup>&</sup>lt;sup>4</sup>En plus de B. Jobstmann, Sergio Yovine (DR) et Stavros Tripakis (CR)

#### CHAPTER 1. GENERAL REPORT

Figure 1.1: Évolution des effectifs non permanents

### 1.4.2 Gouvernance

L'organigramme fonctionnel est donné en annexe B. Le bureau est constitué de la direction (directeur et directeur adjoint) et des responsables d'équipe. Le bureau est réuni chaque fois que des décisions ponctuelles doivent être prises rapidement. Le conseil de laboratoire est réuni tous les 2 mois. Sa composition formelle est donnée en annexe H, mais les séances sont ouvertes à tous les permanents. Les séances du conseil donnent lieu à un compte-rendu. Enfin, une assemblée générale du laboratoire est organisée une fois par an.

#### 1.4.3 Services

Les services sont centralisés.

L'administration est assurée par 4 personnes : une gestionnaire en charge des affaires générales, de la gestion des personnels et du budget, une personne en charge du suivi des contrats, et deux personnes chargées des missions et des commandes. Avec, chaque année, une douzaine d'embauches de contractuels, de l'ordre de 300 missions et 250 commandes, et une vingtaine de contrats en cours, ce service assure des fonctions vitales pour le laboratoire.

Le service informatique est constitué de 2 ingénieurs, en temps normal. Cependant, au cours de la période, ce service a souvent du fonctionner en sous-effectif ou avec des contractuels, du fait du départ d'un ingénieur en 2010 qui n'a été remplacé qu'en 2012, puis d'un autre départ en 2012, qui n'a été remplacé qu'en 2014. Le service gère un parc informatique conséquent (13 serveurs, 246 stations fixes ou mobiles). Certaines fonctionnalités (réseau, messagerie) sont confiées à l'unité mixte de service MI<sup>2</sup>S.

Les ingénieurs de recherche sont affectés aux équipes, dans lesquelles ils participent aux projets, dont ils assurent souvent la gestion, et développent et maintiennent les logiciels issus de la recherche. Ils sont aussi chargés de certaines tâches d'intérêt général, concernant notamment les outils communs.

### 1.4.4 Outils communs

Au fil des années, nous avons développé un certain nombre d'outils pour faciliter la gestion du laboratoire, outils accessibles par l'intranet. Ces développements constituent des tâches d'intérêt général confiées aux ingénieurs de recherche. Nous disposons d'une base de données financières, permettant de gérer et de suivre les contrats quelle que soit la tutelle gestionnaire <sup>5</sup>, d'une base de gestion des effectifs, des locaux et de l'annuaire, d'un outil de demande de mission et de gestion des absences, et d'un outil d'annonce et de suivi des différents séminaires. Au cours de la période, le site Web du laboratoire a été refait, et une base de données des publications a été développée.

<sup>&</sup>lt;sup>5</sup>Quoique le laboratoire soit en délégation globale de gestion financière depuis 2012, il reste quelques projets au CNRS.

#### 1.5. FAITS MARQUANTS

# 1.4.5 Budget, gestion

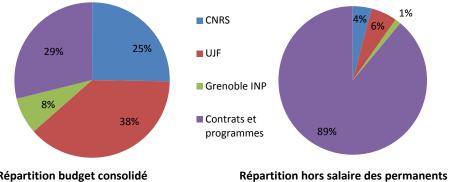

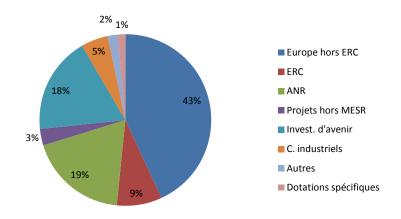

On trouvera le détail des budgets du laboratoire pour 2012 et 2013 dans les tableaux joints au dossier. Pour donner une idée générale, la figure 1.2 donne les montants des ressources 2013 (y compris les salaires des personnels permanents) et leur utilisation. La figure 1.3 donne le détail des ressources propres (89% du budget non consolidé) selon leurs origines.

Le laboratoire prend en charge les dépenses communes : frais d'infrastructure, salaire d'une gestionnaire contractuelle, l'essentiel des dépenses d'équipement et de maintenance, achat de fournitures et de licences de logiciels, missions du directeur et frais de réception. Les ressources propres sont utilisées au niveau des équipes. Selon les années, le laboratoire peut reverser une partie de la dotation aux équipes, ou, au contraire, doit demander aux équipes une participation aux dépenses communes.

Le laboratoire est en délégation globale de gestion financière (DGGF) à l'UJF depuis 2012. A l'époque, il était prévu que tous les laboratoires grenoblois passent en DGGF à l'une de leurs tutelles à brève échéance, et nous avons accepté d'être un laboratoire pilote de ce processus. Cependant, l'expérience n'a pas été poursuivie, et la promesse qui nous avait été faite d'aligner les pratiques de la tutelle gestionnaire sur les meilleures pratiques n'a pas été tenue. Notre demande de revenir en gestion mixte UJF/CNRS, n'a pas eu d'effet jusqu'ici.

## 1.4.6 Locaux

Le laboratoire occupe des locaux de 1440 m<sup>2</sup> appartenant à l'UJF. Au début de la période, ces locaux se composaient du bâtiment Equation-3 et de 2 plates-formes du bâtiment CTL. En 2011, à l'installation du CRI au CTL, le bâtiment Equation-4 a été réhabilité, et les occupants d'une plate-forme du CTL ont déménagé dans la moitié d'Equation-4 (l'autre moitié étant occupée par une équipe du LIG).

# 1.4.7 Animation interne

Le séminaire du laboratoire a lieu assez régulièrement, en moyenne une ou deux fois par mois. On trouvera en annexe I la liste des intervenants pour la période. En plus de ce séminaire général et des réunions des équipes, un séminaire régulier de cryptologie est organisé en collaboration avec d'autres laboratoires concernés (Institut Fourier, LJK, CEA), et un séminaire sur l'analyse de logiciel, commun aux équipes Synchrone et DCS, a vu le jour récemment.

Enfin, depuis 2013, nous organisons annuellement une série de séminaires des doctorants de 2e année (voir  $\S3.1.2$ ).

# 1.5 Faits marquants

En 2012, nous avons eu à déplorer la disparition de Paul Caspi, chercheur d'exception et grande figure du laboratoire. En son honneur, l'ACM SIGBED<sup>6</sup> a créé le "prix de thèse Paul Caspi" qui a été décerné pour la première fois cette année.

**NOE Artist design :** Verimag a été l'instigateur du réseau d'excellence Artist-Design<sup>7</sup>, faisant suite aux réseaux Artist et Artist2. Ces réseaux ont fédéré une vaste communauté de recherche sur la conception des systèmes embarqués en Europe, et ont donné au laboratoire une visibilité européenne et internationale exceptionnelle.

**Start-up Argosim :** Les méthodes de test de logiciels synchrones développées au laboratoire depuis 1998, et expérimentées avec succès dans plusieurs projets (notamment le projet Minalogic COMON, voir page 131), ont conduit à la création d'une start-up en 2013,  $\operatorname{Argosim}^8$ . Voir §2.1.2.3

<sup>&</sup>lt;sup>6</sup>SIGBED est le groupe d'intérêt consacré aux systèmes embarqués de l'Association for Computing Machinery.

<sup>&</sup>lt;sup>7</sup>ww.artist-embedded.org

$<sup>^{8}</sup>$ www.argosim.com

# CHAPTER 1. GENERAL REPORT

|                        | Total     | Fonctionnement | Salaires  |

|------------------------|-----------|----------------|-----------|

| Total établissements   | 3 508 155 | 149 180        | 3 358 975 |

| CNRS                   | 1 246 044 | 65 000         | 1 181 044 |

| UJF                    | 1 886 776 | 64 180         | 1 822 596 |

| Grenoble INP           | 375 335   | 20 000         | 355 335   |

| Contrats et programmes | 1 424 936 | 679 748        | 745 187   |

| Total                  | 4 912 861 | 808 699        | 4 104 162 |

Répartition budget consolidé

Figure 1.2: Budget consolidé 2013

|                       | Total     | Fonctionnement | Salaires |

|-----------------------|-----------|----------------|----------|

| Europe hors ERC       | 614 207   | 349 508        | 264 699  |

| ERC                   | 121 192   | 66 019         | 55 173   |

| ANR                   | 265 183   | 88 655         | 176 528  |

| Projets hors MESR     | 44 285    | 34 783         | 9 502    |

| Invest. d'avenir      | 259 979   | 41 518         | 218 461  |

| C. industriels        | 72 802    | 61 215         | 11 587   |

| Autres                | 27 289    | 18 052         | 9 237    |

| Dotations spécifiques | 19 999    | 19 999         | 0        |

| Tota                  | 1 424 936 | 679 748        | 745 187  |

Figure 1.3: Détail des ressources propres 2013

# 1.6. AUTO-ÉVALUATION

**Projet ERC STATOR :** David Monniaux, DR CNRS de l'équipe Synchrone, a obtenu un projet ERC "Starting investigator" sur l'analyse statique des programmes (voir  $\S2.1.2.2$ ). Ce projet, doté d'un budget de 1472 k€, se déroule de 2013 à 2017.

**Organisation de grandes conférences :** Verimag a organisé plusieurs événements importants, en particulier la conférence CAV 2009 (Computer Aided Verificationi<sup>9</sup>) — principale conférence internationale sur la vérification automatisée — et surtout ETAPS 2014, (European Joint Conferences on Theory and Practice of Software<sup>10</sup>), qui est un des principaux événements scientifiques concernant les méthodes de développement du logiciel : regroupant 6 conférences internationales et plus de 20 workshops, ETAPS 2014 a attiré près de 800 participants.

**Pour célébrer les 20 ans de Verimag** nous avons organisé trois journées scientifiques, les 26, 27 et 28 septembre 2012, où nous avons invité un pannel d'orateurs prestigieux :

| Gilles Barthe (IMDEA)                 | Ahmed Bouajjani (LIAFA, Paris)   |

|---------------------------------------|----------------------------------|

| Luca Benini (Università di Bologna)   | Tom Henzinger (IST Austria)      |

| Albert Benveniste (Inria, Rennes)     | Joseph Sifakis (EPFL et Verimag) |

| Gérard Berry (Collège de France)      | Parvin Varaiya (Berkeley)        |

| Reinhard Wilhelm (Sa                  | aarland University)              |

| · · · · · · · · · · · · · · · · · · · |                                  |

Ces journées ont attiré une soixantaine de participants.

**"Best papers" :** Meilleur article pour Jannik Dreier à la Third IEEE International Conference on Information Privacy, Security, Risk and Trust [**D-C111**] ; Meilleur article pour Stéphane Devismes, Karel Heurtefeux et Yvan Rivierre à ICNC'2011 [**S-C47**] ; Meilleur article pour Radu Iosif à CADE 2013 [**D-C19**] ; Meilleur article d'étudiant pour Yvan Rivierre à SSS'2013 [**S-C13**].

**Distinctions** Joseph Sifakis a été élu à l'Académie des Sciences en 2011, et nommé Commandeur de la Légion d'Honneur en 2012. Nicolas Halbwachs a été élu à l'Academia Europaea en 2010. En 2010, le projet MARAE a été distingué par la Fondation de Recherche pour l'Aéronautique et l'Espace (FRAE), et, à cette occasion, Saddek Bensalem a reçu un des trois prix de la meilleure publication scientifique des programmes de recherche.

# 1.6 Auto-évaluation

## 1.6.1 Forces

La principale force de Verimag est la qualité de sa production scientifique et sa visibilité internationale. La qualité des publications est attestée par de nombreuses références : par exemple, plus de 40% des articles publiés dans la conférence EMSOFT'2013 citent au moins une publication de Verimag, et les publications citées datent presque toutes de moins de 10 ans. Le rayonnement du laboratoire apparaît en particulier dans notre forte présence dans les comités de programme des conférences et workshops (123 comités pour la période, dont 4 co-présidences de comités de conférences majeures); nous avons aussi organisé de très nombreux événements et écoles (voir  $\S D.1.2$ ).

La cohérence scientifique du laboratoire est un atout : Verimag réunit des compétences complémentaires sur des sujets variés, mais tous reliés à un domaine bien délimité. Les coopérations entre les différents groupes sont réelles et fructueuses. Les thématiques se sont diversifiées, mais sans dispersion.

La synergie entre les recherches fondamentales et les applications est une réalité. Les collaborations industrielles directes sont généralement limitées à des contrats CIFRE, mais souvent poursuivies sur le long terme. Par ailleurs, nous avons de nombreuses collaborations industrielles dans le cadre de projets (Europe, ANR, pôles de compétitivité).

<sup>&</sup>lt;sup>9</sup>www-cav2009.imag.fr/

$<sup>^{10} {\</sup>rm www.etaps.org}$

#### CHAPTER 1. GENERAL REPORT

L'encadrement des doctorants est de bonne qualité : il y a eu, certes, 5 abandons sur la période, mais 3 d'entre-eux ont eu lieu en fin de 1ère année, les deux autres correspondant à des embauches avant la fin de la thèse. Par ailleurs, nos docteurs se placent bien; sur 36 doctorants diplômés pendant la période, aucun n'est en recherche d'emploi : 11 ont obtenu des situations académiques, 16 sont dans l'industrie, 8 sont en postdoctorat, 1 est en sabbatique.

Enfin, un changement de génération est en cours, de manière satisfaisante. De jeunes chercheurs et enseignants-chercheurs prennent des responsabilités (encadrement, coordination de projets, passage de HDR), et le remplacement de la direction (directeur, responsables d'équipe) est prêt.

#### 1.6.2 Faiblesses

Le nombre de thèses encadrées est assez variable, et peut être jugé faible, au regard des capacités d'encadrement. La difficulté de recruter des doctorants — qu'il faut souvent attirer par des stages des années à l'avance — et un certain élitisme en sont la cause. La durée des thèses est longue, mais dans la moyenne de l'Ecole doctorale, et les doctorants sont financés sur cette durée.

L'évolution des thématiques rend quelque peu caduques le périmètre et la cohésion des équipes, c'est pourquoi une restructuration du laboratoire sera proposée dans le projet.

Il reste des enseignants peu impliqués dans la recherche, mais certains de ceux qui étaient dans ce cas en début de période se sont ré-investis dans des projets et se sont remis à publier.

Nous continuons d'avoir de grandes difficultés à recruter au CNRS. En 2012, un candidat du laboratoire a été bien classé, mais a préféré une grande université américaine; en 2014, une excellente candidate n'a pas été classée en section 06, avant d'être recrutée 1ère sur un poste Inria !

## 1.6.3 Opportunités

Le nouveau bâtiment PILSI, en construction dans le cadre du plan "Campus", devrait accueillir, en 2016, les 3 laboratoires LIG, LJK et Verimag, ainsi que l'unité de service MI<sup>2</sup>S. Non seulement, nous espérons que ces nouveaux locaux seront plus propices à notre activité, mais la proximité immédiate d'autres équipes de recherche en informatique et en mathématiques appliquées ouvre aussi des perspectives de coopération scientifique ainsi que de synergie entre les services. Sur ce dernier point, la réflexion est déja bien avancée entre les 3 laboratoires.

Nous espérons que la construction d'une grande université Grenoble-Alpes donnera une meilleure visibilité internationale au site, et ouvrira une ère de relations apaisées entre nos tutelles. La structuration en pôles thématiques est tout-à-fait adéquate, et Verimag trouve naturellement sa place au sein du pôle MSTIC.

#### 1.6.4 Menaces

Le détachement de 3 chercheurs CNRS et d'un enseignant-chercheur représente une vraie perte de potentiel. En particulier, le thème de l'analyse de protocoles cryptographiques est affaibli, d'autant que Yassine Lakhnech est moins présent du fait de ses fonctions de vice-président recherche de l'UJF. Cette perte de potentiel risque fort de perdurer, avec la réduction drastique des créations de postes universitaires, et nos difficultés à recruter au CNRS.

Le déménagement au campus ouest du groupe BIP avec le CRI est évidemment un risque pour la cohésion du laboratoire.

Le passage en DGGF est un handicap pour le laboratoire. Il serait temps que les tutelles reconnaîssent que cette démarche est un échec.

# Chapter 2

# Detailed scientific report Présentation détaillée

# 2.1 Synchrone team

# 2.1.1 Synchrone team: Scientific production

The main scientific topics of the team during the period are:

- 1. Modeling and simulation for systems-on-a-chip and networks of embedded systems; trade-off between efficiency and precision/faithfulness in models and simulation tools;

- 2. Distributed algorithms, in particular self-stabilizing ones, applications to security in sensor networks

- 3. Foundations of, tools for, and applications of abstract interpretation, decision procedures

- 4. Languages and methods for the **automatic testing** of embedded reactive systems

- 5. Implementation and analysis methods for critical embedded systems, in particular worst-caseexecution-time analysis (WCET) and real-time calculus; energy-aware implementations for embedded systems; recent focus on manycore hardware platforms.

The work on simulation and modeling for sensor networks, and the work on distributed algorithms applied to security in sensor networks, have been done in the context of the two ANR projects ARESA and ARESA2 (see pages 140 and 126), together with L. Mounier and P. Lafourcade of the DCS team, and in collaboration with Orange Labs. The work on modeling and simulation for systems-on-a-chip is done in the context of a long-lasting collaboration with STMicroelectronics. The work on manycore architectures is done in collaboration with S. Mancini from the TIMA laboratory, and Kalray. We also started quite recently (November, 2013) a collaboration with Orange Labs in Grenoble, and Didier Donsez from the LIG laboratory, about smart cities. A CIFRE PhD student (L. Lemke, see page 160) works on the formal models that are needed for the deployment of software onto the devices of the smart city, in the context of shared and open infrastructures.

In the last five years, the team has fully integrated the work on distributed algorithms and systems, and the work on worst-case-execution-time analysis (we lead the ANR project W-SEPT, page 114). The work on hardware architectures has converged with the work on programming languages for critical systems, allowing us to participate in the national project CAPACITES led by Kalray, where we propose to study the implementation of dataflow synchronous formalisms on the manycore platform proposed by the company, in close collaboration with end users like Airbus, Eurocopter, Dassault Aviation, etc. The work on abstract interpretation has evolved into a well identified activity, including fundamental work on the core of abstract interpreters (ANR ASOPT project, page 132) and new directions like the certification of tools (ANR VERASCO project, page 115, together with members of the DCS team), and the application to WCET. D. Monniaux has obtained an ERC grant on research of new approaches in combinations of abstract interpretation and satisfiability testing (STATOR, page 109).

#### 2.1.1.1 Modeling and simulation

The development of complex hardware/software embedded systems, and networks of embedded systems, faces several problems: the cost of the final object to be developed, either a system-on-a-chip (SoC), or a deployment in the field for, e.g., sensor networks; the lack of observability means for this final object; and its late availability. This is the reason why the properties of the hardware/software systems are most of the time assessed by simulations, using a system-level model, also called *virtual prototype* (VP). The VP is an executable model, and simulations are performed with discrete-event simulation engines, typically. Hardware companies have adopted SystemC and Transaction-Level Modeling (TLM) for SoCs. As in any context where modeling and simulation are used, a trade-off has to be found between the precision of the model, and the speed of the simulation. We worked on several aspects related to this trade-off. We also extended previous work to include non-functional properties: energy consumption and temperature in SoCs, security in sensor networks.

In the openTLM project (see page 141), we worked on compilation techniques and formal verification of SystemC. A new tool called PinaVM includes a compiler front-end [S-C77] [S-C76] and a back-end [S-C58] able to generate code for the model-checker SPIN. PinaVM is internally based on the "static single assignment representation" (SSA), which we showed allows an efficient encoding [S-C84]. PinaVM is also used for purposes other than verification like optimized compilation.

In the ANR project HELP (see page 125), we proposed a general instrumentation method that adds energy consumption information to a functional TLM model (in the form of *power-state* or *traffic* models); we defined an efficient co-simulation method, with a temperature simulator [S-C27] [S-C9] [S-C10] (either ATMI, or the tool ACEplorer developed by the partner DOCEA Power). The libraries developed in the project are available as free software; the principles of the instrumentation and the cosimulation have been implemented by the industrial partners, in their design flow. We worked on the coupling between modeling principles and implementations of the simulation engine, in order to get significant improvements of the simulation speed. We proposed to augment TLM models with a notion of *task with duration*, first in Java with jTLM [S-C53] [S-C52], and then as a conservative extension of SystemC that allows parallel executions [S-C20], without changing the behavior of the existing models that do not use the extension. This is a very promising approach, compatible with existing TLM models (contrary to approaches like TLM-DT that require an entire rewrite of the models) and offering more potential for parallelization than other approaches targetting the simulation engine only; the topic continues in the openES project (page 109). We also worked on temporal decoupling to improve simulation speed even in the sequential case [S-C17].

We developed the component model 42 (PhD of T. Bouhadiba, page 158, [S-P7]), inpired by Ptolemy, as a means to study models of communication and computation (MoCCs). The "42ization" of SystemC [S-C80] was a first step towards system-level models of SoCs, in which some components may be known only by very abstract but formalized specifications (given by *contracts* for instance); these formal contracts, together with the semantics of an assemblage of components, allows to "execute" a system at a very early stage of development. We continue this topic in the openES project (page 109), in the wider context of functional and extra-functional properties (like energy-consumption and temperature, studied in the project HELP).

In the context of a CIFRE PhD with STMicroelectronics (G. Funchal, page 158), we studied memory models [S-C51], and how to include them in the TLM models that serve for the development of low-level software in SoCs. We proposed to abstract the detailed behavior of the memory hierarchy by non-deterministic models, able to show the memory bugs of the low-level software.

In the context of the ANR projects ARESA and ARESA2 (pages 140 and 126), we proposed simulation models for energy consumption in sensor networks; the simplest models are based on the "joule-per-bit" abstraction, relating the energy consumption to the number of bits transmitted; this is implementable in any simulator. Since this abstraction hides the cost of *idle listening*, it is sometimes necessary to augment the model with some information on the state of the hardware, especially the radio component. This requires a significant change in the simulation models, and the definition of manageable abstractions, for a reasonable simulation speed. We defined such models, first using tools of the synchronous community, and then using tools of the sensor network community; the comparison between models and real measurements will be finally possible in collaboration with Orange labs, in the context of a CIFRE PhD starting in 2014. In ARESA2, our main topic was the trade-off between energy consumption and security (see also section 2.1.1.2); as far as modeling is concerned, we studied and implemented the attacker models.

#### 2.1. SYNCHRONE TEAM

#### 2.1.1.2 Distributed algorithms

This topic aims at providing new solutions for modern networks, such as Wireless Sensor Networks (WSNs). These networks are resource-constrained, large-scale, and fault-prone. The work consists in designing distributed algoritms, in particular probabilistic ones. We validate our solutions using formal analysis and simulations.

During the last four years, we followed several directions, including the design and analysis of self-stabilizing, probabilistic, and/or secure algorithms.

Concerning the self-stabilizing topic, most of our work has been done as part of the PhD thesis of Yvan Rivierre [S-J12, S-C28, S-J3, S-C13, S-J4], this latter dealing with distributed spanning structures. The remainder of the work deals with properties related to self-stabilization [S-C94, S-C83, S-C91, S-J16, S-J17, S-C65, S-C70, S-J15, S-C71, S-C42, S-C32]. Especially, we proposed new fault-tolerant properties and solutions [S-C2]. Concerning the probabilistic topic, we analytically study random walk protocols [D-C42, D-J3]. We have evaluated the performances of various types of random walk, in particular self-avoiding and biased random walks.

Finally, we designed in [D-C17] resilient versions of the tabu random walks to solve secure convergecast routing in WSNs prone to insider attacks. Our solution uses some classical lightweight cryptographic mechanisms to ensure data confidentiality, integrity, and authenticity. Then, we introduce an original self-adaptive reputation mechanism to maintain an interesting delivery rate. This work has been done as part of the ANR project ARESA2 (page 126). The point of view of fault-tolerance allowed us to answer the question of attackers in sensor networks. This is a problem in itself, because the Dolev-Yao hypothesis of an attacker that can do anything but decrypt messages without the key, is far too strong for sensor networks. We have to limit the power of attackers, and decide beforehand what type of attacks a sensor network can resist.

### 2.1.1.3 Decision procedures and abstract interpretation

The semantics of finite unfoldings of program executions can be expressed as first-order formulas over arithmetic or extensions thereof. Many verification approaches therefore use *decision procedures* to check whether such formulas hold, or *satisfiability testing* to get solutions (models). Such solutions often express *counterexamples* to purported properties or inductive invariants: in many approaches, solutions directly map to counterexample traces that can be reported back to the user (in case of a trace from an initial state to an error state) or fed back to a refinement procedure. It is therefore of paramount importance that decision procedures are efficient in practice, even in cases known to have high worst-case complexity (e.g. quantifier alternation), despite the progresses made in *satisfiability modulo theory* (SMT) since 2000.

We have researched efficient procedures for decision [S-C26] and *quantifier elimination* in linear arithmetic [S-C75, S-C38]. With respect to quantifier-free formulas generated from program semantics, we have researched partial abstractions, which dramatically improve the performance of SMT-solver in the case of formulas arising from worst-case execution time analysis (WCET) [S-C1].

Outside of certain very restricted classes of programs, reachability after an unbounded number of program steps is a undecidable problem. Abstract interpretation is an approach to static analysis where sets of reachable states, too difficult to represent exactly, are over-approximated by symbolic sets on which it is possible to compute; the final result of an analysis by abstract interpretation is generally an *inductive invariant* chosen within a specific *abstract domain* (e.g. products of intervals or convex polyhedra, for numerical properties).

Traditionally, abstract interpretation computes inductive invariants as the limit of an ascending *Kleene iteration* sequence, accelerated using *widening* operators. Widenings are a known cause of imprecision (leading to false positives) and of non-monotonicity (better knowledge of the system may lead to more false positives); we have researched methods for computing the exact limit, based on quantifier elimination [S-J18] and policy iteration [S-C54, S-J8]. We proposed also a method to improve fixpoints obtained by widening-narrowing [S-C33]. Another source of imprecision is the enforced approximation into the abstract domain at every program location; we bypass it using implicit path enumeration by SMT-solving [S-J8, S-C35, S-C34, S-C54, S-C61, S-J18].

One criticism of formal methods is that the tools (e.g. static analyzers) may themselves contain bug: how much can we trust their results? We have therefore investigated the construction of static analysis tool fully proved correct within the Coq proof assistant, relying on a constraint-only representation of convex polyhedra [S-C11, D-C34].

#### 2.1.1.4 Automatic testing

During the last decade, the team worked on stochastic extensions of synchronous languages. The motivation is to simulate the (physical) environment of a reactive system. Reactive systems and programs are particular, in that they usually function in a closed loop with their environment. Simulating the environment is compulsory to be able to test reactive programs with realistic inputs.