# UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Mathématiques et Informatique

Arrêté ministériel : 25 mai 2016

Présentée par

### **Thomas Ferrère**

Thèse dirigée par Oded Maler

préparée au sein du laboratoire Verimag et de l'école doctorale Mathématiques, Sciences et Technologies de l'Information et l'Informatique

# Assertions and Measurements for Mixed-Signal Simulation

Thèse soutenue publiquement le **28 octobre 2016**, devant le jury composé de :

Prof. Ahmed Bouajjani Université Paris 7, Président **Dr. Jyotirmoy Deshmukh** Toyota, Rapporteur **Prof. Javier Esparza** Université technique de Munich, Rapporteur **Prof. Thomas Henzinger** IST Austria, Examinateur Dr. Dejan Nickovic Austrian Institute of Technology, Examinateur Prof. Alberto Sangiovanni-Vincentelli Université de Californie à Berkeley, Examinateur Dr. Oded Maler CNRS, Directeur de thèse Dr. Ernst Christen Mentor Graphics, Co-encadrant

# Acknowledgements

I must start by thanking my supervisor, Oded Maler, whose benevolent guidance, support, encouragement, and trust were essential to this thesis being what it is – tautology intended. Working alongside Oded was a stimulating and rewarding experience, and I learned a great deal in the process, from theoretical to practical aspects of research.

I am also indebted to my co-advisor, Ernst Christen, who spared countless hours explaining, discussing, debating, and challenging conceptions that I came to form about the mixed-signal domain. Ernst's top-down approach to research ensured a complementary, somewhat reverse-engineered flow from practice to theory. I thank both Ernst and Oded for the attention they devoted to proof-reading manuscript drafts.

I was privileged to be read and heard by a jury totaling eight researchers and professors, to whom I am very grateful. I thank Ahmed Bouajjani, Jyo Deshmukh, and Javier Esparza for their careful reading and commenting of the manuscript, which gave me the opportunity to further improve its quality. I thank Tom Henzinger, Dejan Nickovic, and Alberto Sangiovanni-Vincentelli for their in-depth questions and remarks, some of which already led to new research directions being investigated.

Let me take this opportunity to thank other colleagues in relation with my two host institutions: the ADMS team of Mentor Graphics Corporation, and the Verimag laboratory of Grenoble University.

In Mentor Graphics, I would like to thank Jean-Marc Talbot for providing both highlevel oversight and in-depth remarks during regular progress meetings. I am grateful to Martin Vlach for contributing to the initial research proposal. Polen Kission was responsible for the early orientation of the applicative focus of my research, and furthermore took part throughout in ensuring its timely progression. Thank you Polen for enabling the thesis to run smoothly. Among other Mentor colleagues, the help of Serge Garcia-Sabiro and Eric Jeandeau was instrumental in its provision of realistic use-cases and the sharing of their related applicative research. Serge also gave feedback on my own research efforts. I thank all the ADMS team for their availability in providing technical help and creating the friendly atmosphere, in which it was very enjoyable to work.

In Verimag, my research benefited from the following interactions with present or (distant) past members. I thank Alexandre Donzé for involving me into what would become a first scientific publication. Dejan Nickovic collaborated formally and informally on many projects. Thank you Dejan for also inviting me to the Austrian Institute of Technology in July 2015. I am grateful to Eugene Asarin for making accessible his knowledge in various domains, and for giving detailed feedback on several early research drafts. I would also like to thank Dogan Ulus for our fruitful collaboration; proving me wrong more than once, and seeing opportunity where I was doubtful of my own solution.

In general I must acknowledge the important role of other fellow PhD candidates in improving the quality of my scientific and social life! I thank all Verimag researchers, in particular its successive directors Nicolas Halbwachs and Florence Maraninchi for providing all the assistance I ever needed.

This is also for me the occasion to thank, and acknowledge the role of previous professors who introduced me to the domain of formal verification and monitoring, Arnaud Durand and Nicolas Rapin.

Science sans conscience n'est que ruine de l'âme... To finish I warmly thank all my family, who continuously supported me through this (sometimes consuming) process. Most especially to my wife Lorna, thank you for standing by my side all those years.

# Abstract

This thesis is concerned with the monitoring of mixed-signal circuit simulations. In the field of hardware verification, the use of declarative property languages in combination with simulation is now standard practice. However the lack of features to specify asynchronous behavior, or the insufficient integration of verification results, makes existing assertion and measurement languages unusable in the mixed-signal setting.

We propose several theoretical and practical tools for the description and automatic monitoring of such behaviors, that feature both discrete and continuous aspects. For this we build on previous work on real-time extensions of temporal logic and regular expressions as follows.

Efficient algorithms for computing the distance from some simulation trace to temporal logic specifications are given, with complexity comparable to that of traditional monitoring. An original diagnostic procedure is provided for the systematic debugging of such traces. The monitoring of continuous behaviors is also extended to other forms of assertions based on regular expressions. These expressions form the basis of our measurement language, which describes conjointly a measure and the patterns over which that measure should be taken.

We finish by showing how measurements currently implemented in analog circuits simulators can be ported to digital descriptions, this way extending structured verification methodologies used for digital designs toward mixed-signal.

# Résumé

L'objet de cette thèse est le monitorage des simulations de circuit en signaux mixtes analogique / digital. Dans le domaine de la vérification de matériel, l'utilisation de langages déclaratifs pour la description de propriété, combinés avec la simulation, est dorénavant pratique courante. Cependant, par absence de fonctionalités dédiées à la spécification de comportement asynchrones, ou dû à l'intégration insuffisante des résultats de vérification, les assertions et mesures telles que couramment implantées sont presque inutilisables dans un contexte de signaux mixtes.

Nous proposons plusieurs outils théoriques et pratiques pour la formalisation et le monitorage de tels comportements, à la jonction de mondes discret et continu. Pour ce faire, nous nous appuyons sur des recherches antérieures dans le domaine des spécifications temps-réel, particulièrement en ce qui concerne la logique temporelle et les expressions régulières, et obtenons les résultats suivants.

Des algorithmes pour calculer la distance d'une trace de simulation à une propriété de logique temporelle sont décrits; ils garantissent une complexité comparable à celle du problème de monitorage correspondant. Une procédure originale pour le débogage systématique d'une telle trace relativement à une formule de logique temporelle est donnée. Le monitorage des comportements continus est ensuite étendu à d'autres formes d'assertions, basées sur les expressions régulières. Ces expressions forment la base de notre langage de description de mesures, qui permet de spécifier conjointement des intervalles temporels à observer et un certain type de mesure à appliquer.

Nous montrons enfin comment étendre le champ d'application des outils de mesure existant dans un simulateur de circuits analogiques, pour une utilisation dans les descriptions digitales. Ce faisant, nous rendons possible l'utilisation des méthodologies de vérification hiérarchiques venant du monde digital dans un contexte de signaux mixtes.

# Contents

| Introduction 1              |                                                                     |                                                   |          |  |  |  |  |  |  |

|-----------------------------|---------------------------------------------------------------------|---------------------------------------------------|----------|--|--|--|--|--|--|

| 1                           | Mix                                                                 | ixed-Signal Verification                          |          |  |  |  |  |  |  |

|                             | 1.1                                                                 | Circuit Design                                    | 6        |  |  |  |  |  |  |

|                             | 1.2                                                                 | Modeling                                          | 7        |  |  |  |  |  |  |

|                             | 1.3                                                                 | Simulation                                        | 9        |  |  |  |  |  |  |

|                             | 1.4                                                                 | Verification                                      | 10       |  |  |  |  |  |  |

|                             |                                                                     | 1.4.1 Digital                                     | 10       |  |  |  |  |  |  |

|                             |                                                                     | 1.4.2 Analog                                      | 10       |  |  |  |  |  |  |

|                             |                                                                     | 1.4.3 Mixed-Signal                                | 11       |  |  |  |  |  |  |

|                             | 1.5                                                                 | Measurements                                      | 12       |  |  |  |  |  |  |

|                             | 1.6                                                                 | Assertions                                        | 12       |  |  |  |  |  |  |

| 9                           | Cmo                                                                 | sifting Discrete and Continuous Dronarties        | 16       |  |  |  |  |  |  |

| 2                           | 2 Specifying Discrete and Continuous Properties<br>2.1 Introduction |                                                   |          |  |  |  |  |  |  |

|                             | 2.1<br>2.2                                                          | Introduction                                      | 16<br>17 |  |  |  |  |  |  |

|                             | 2.2                                                                 | 2.2.1 Signals                                     | 17       |  |  |  |  |  |  |

|                             |                                                                     | 2.2.1 Signals                                     | 18<br>18 |  |  |  |  |  |  |

|                             |                                                                     | 2.2.2 Variables                                   | 10<br>19 |  |  |  |  |  |  |

|                             |                                                                     | 2.2.4 Events                                      | 19       |  |  |  |  |  |  |

|                             |                                                                     | 2.2.4       Events                                | 19<br>20 |  |  |  |  |  |  |

|                             | 2.3                                                                 | 1                                                 | 20<br>21 |  |  |  |  |  |  |

|                             | 2.3                                                                 | Declarative Property Languages2.3.1Temporal Logic | 21<br>21 |  |  |  |  |  |  |

|                             |                                                                     | 1 0                                               | 21<br>22 |  |  |  |  |  |  |

|                             |                                                                     | <b>1</b>                                          | 22<br>24 |  |  |  |  |  |  |

|                             |                                                                     | 1 1                                               | 24<br>25 |  |  |  |  |  |  |

|                             |                                                                     | 2.3.4 Timed Properties                            | 25       |  |  |  |  |  |  |

| 3 Temporal Logic Monitoring |                                                                     |                                                   | 27       |  |  |  |  |  |  |

|                             | 3.1                                                                 |                                                   | 27       |  |  |  |  |  |  |

|                             | 3.2                                                                 | Metric Temporal Logic                             | 28       |  |  |  |  |  |  |

|                             |                                                                     | 3.2.1 Syntax and Semantics                        | 28       |  |  |  |  |  |  |

|                             |                                                                     | 3.2.2 Until Rewrite                               | 29       |  |  |  |  |  |  |

|                             |                                                                     | 3.2.3 Satisfaction Signals                        | 29       |  |  |  |  |  |  |

|                             | 3.3                                                                 | Interval Marking                                  | 30       |  |  |  |  |  |  |

|                             | 3.4                                                                 | Algorithms                                        | 32       |  |  |  |  |  |  |

| 4 | Diagnostics |        |                                                             |  |  |  |  |

|---|-------------|--------|-------------------------------------------------------------|--|--|--|--|

|   | 4.1         | Introd | uction                                                      |  |  |  |  |

|   |             | 4.1.1  | Motivation                                                  |  |  |  |  |

|   |             | 4.1.2  | Our Approach 36                                             |  |  |  |  |

|   |             | 4.1.3  | Related Work    37                                          |  |  |  |  |

|   | 4.2         | Propos | sitional Foundations                                        |  |  |  |  |

|   |             | 4.2.1  | Problem Statement                                           |  |  |  |  |

|   |             | 4.2.2  | Syntactic and Semantic Formulations                         |  |  |  |  |

|   |             | 4.2.3  | Practical Solution                                          |  |  |  |  |

|   | 4.3         | Tempo  | oral Implicants                                             |  |  |  |  |

|   |             | 4.3.1  | Semantics                                                   |  |  |  |  |

|   |             | 4.3.2  | Syntax 40                                                   |  |  |  |  |

|   |             | 4.3.3  | Minimality 41                                               |  |  |  |  |

|   | 4.4         | Comp   | utation                                                     |  |  |  |  |

|   |             | 4.4.1  | Metric Temporal Logic 43                                    |  |  |  |  |

|   |             | 4.4.2  | Non-Standard Semantics                                      |  |  |  |  |

|   |             | 4.4.3  | Explanation Operators 45                                    |  |  |  |  |

|   |             | 4.4.4  | Selection Functions                                         |  |  |  |  |

|   |             | 4.4.5  | <b>Evaluation</b>                                           |  |  |  |  |

| _ | Dala        |        |                                                             |  |  |  |  |

| 5 | <b>KOD</b>  |        | s Analysis 52<br>uction                                     |  |  |  |  |

|   | 5.2         |        | Temporal Logic         52           54         54           |  |  |  |  |

|   | 5.4         | 5.2.1  | Qualitative Semantics   54                                  |  |  |  |  |

|   |             | 5.2.1  | Quantitative Semantics   55     Quantitative Semantics   55 |  |  |  |  |

|   |             | 5.2.3  | Robustness Estimate       56                                |  |  |  |  |

|   |             | 5.2.4  | Until Rewrite                                               |  |  |  |  |

|   | 5.3         |        | vise Linear Decomposition                                   |  |  |  |  |

|   | 5.5         | 5.3.1  | Propositional Operators                                     |  |  |  |  |

|   |             | 5.3.2  | Temporal Operators                                          |  |  |  |  |

|   | 5.4         |        | thms                                                        |  |  |  |  |

|   | Ј.т         |        | Timed Eventually                                            |  |  |  |  |

|   |             | 5.4.2  | Untimed Until                                               |  |  |  |  |

|   | 5.5         | ···-   | ation                                                       |  |  |  |  |

|   | 5.5         | 5.5.1  | Complexity                                                  |  |  |  |  |

|   |             | 5.5.2  | Experiments                                                 |  |  |  |  |

|   |             | 5.5.2  |                                                             |  |  |  |  |

| 6 | •           |        | pressions Monitoring 67                                     |  |  |  |  |

|   | 6.1         |        | uction                                                      |  |  |  |  |

|   |             | 6.1.1  |                                                             |  |  |  |  |

|   |             | 6.1.2  | Our Approach   68                                           |  |  |  |  |

|   |             | 6.1.3  | Related Work   69                                           |  |  |  |  |

|   | 6.2         | Timed  | Regular Expressions69                                       |  |  |  |  |

|   |             | 6.2.1  | Syntax and Semantics                                        |  |  |  |  |

|   |             | 6.2.2  | Match Set                                                   |  |  |  |  |

|   | 6.3         | Zone I | Marking                                                     |  |  |  |  |

|    | 6.4           | Algorithms                                                                                                                                                                                                        | 75                          |  |  |  |  |  |  |  |  |  |

|----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|--|--|--|--|

|    |               | 6.4.1 Zones Computation                                                                                                                                                                                           | 75                          |  |  |  |  |  |  |  |  |  |

|    |               | 6.4.2 A Bound for the Kleene Star                                                                                                                                                                                 | 77                          |  |  |  |  |  |  |  |  |  |

|    | 6.5           | Integration with Temporal Logic                                                                                                                                                                                   | 79                          |  |  |  |  |  |  |  |  |  |

|    | 6.6           | Evaluation                                                                                                                                                                                                        | 80                          |  |  |  |  |  |  |  |  |  |

| 7  | Patt          | Pattern-Based Measurements 82                                                                                                                                                                                     |                             |  |  |  |  |  |  |  |  |  |

|    | 7.1           |                                                                                                                                                                                                                   | 82                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 82                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 83                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 83                          |  |  |  |  |  |  |  |  |  |

|    | 7.2           |                                                                                                                                                                                                                   | 84                          |  |  |  |  |  |  |  |  |  |

|    | /             | 0 0 1                                                                                                                                                                                                             | 84                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 85                          |  |  |  |  |  |  |  |  |  |

|    | 7.3           |                                                                                                                                                                                                                   | 85                          |  |  |  |  |  |  |  |  |  |

|    | 7.0           |                                                                                                                                                                                                                   | 85                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 86                          |  |  |  |  |  |  |  |  |  |

|    | 7.4           |                                                                                                                                                                                                                   | 87                          |  |  |  |  |  |  |  |  |  |

|    | 7.4           |                                                                                                                                                                                                                   | 87                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 87<br>89                    |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 89<br>89                    |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 89<br>90                    |  |  |  |  |  |  |  |  |  |

|    |               | 7.4.4 Results                                                                                                                                                                                                     | 90                          |  |  |  |  |  |  |  |  |  |

| 8  |               | 8                                                                                                                                                                                                                 | 92                          |  |  |  |  |  |  |  |  |  |

|    | 8.1           |                                                                                                                                                                                                                   | 92                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 92                          |  |  |  |  |  |  |  |  |  |

|    |               | 11                                                                                                                                                                                                                | 93                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 94                          |  |  |  |  |  |  |  |  |  |

|    | 8.2           | Preliminaries                                                                                                                                                                                                     | 94                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 94                          |  |  |  |  |  |  |  |  |  |

|    |               | 8.2.2 Interaction with Environment                                                                                                                                                                                | 96                          |  |  |  |  |  |  |  |  |  |

|    | 8.3           | Visible Objects                                                                                                                                                                                                   | 97                          |  |  |  |  |  |  |  |  |  |

|    |               | 8.3.1 Set of Functions                                                                                                                                                                                            | 97                          |  |  |  |  |  |  |  |  |  |

|    |               | 8.3.2 Task                                                                                                                                                                                                        | 98                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 90                          |  |  |  |  |  |  |  |  |  |

|    |               |                                                                                                                                                                                                                   | 90<br>99                    |  |  |  |  |  |  |  |  |  |

|    |               | 8.3.3 Module                                                                                                                                                                                                      |                             |  |  |  |  |  |  |  |  |  |

|    | 8.4           | 8.3.3         Module            8.3.4         Class                                                                                                                                                               | 99                          |  |  |  |  |  |  |  |  |  |

|    | 8.4           | 8.3.3       Module       9         8.3.4       Class       9         Implementation       1                                                                                                                       | 99<br>99                    |  |  |  |  |  |  |  |  |  |

|    | 8.4           | 8.3.3       Module       9         8.3.4       Class       9         Implementation       1         8.4.1       Core       1                                                                                      | 99<br>99<br>00              |  |  |  |  |  |  |  |  |  |

|    |               | 8.3.3       Module       9         8.3.4       Class       9         Implementation       1         8.4.1       Core       1         8.4.2       Wrappers       1                                                 | 99<br>99<br>00<br>00        |  |  |  |  |  |  |  |  |  |

| Со |               | 8.3.3       Module       9         8.3.4       Class       9         Implementation       1         8.4.1       Core       1         8.4.2       Wrappers       1         Case Study       1                      | 99<br>99<br>00<br>00<br>.01 |  |  |  |  |  |  |  |  |  |

|    | 8.5<br>onclus | 8.3.3       Module       4         8.3.4       Class       1         Implementation       1         8.4.1       Core       1         8.4.2       Wrappers       1         Case Study       1         sion       1 | 99<br>99<br>00<br>00<br>.01 |  |  |  |  |  |  |  |  |  |

# Introduction

#### Context

Complex engineered systems such as integrated circuits are designed using *models* that describe the behavior of their components in a mechanistic way. These models are then used to simulate various scenarios of the behavior of the system in question; designers monitor the simulated behavior in order to evaluate the system's performance and conformance to specifications. As systems tend to be larger and more complex, simulation becomes more expensive, the number of possible scenarios grows, and the criteria according to which behaviors are evaluated also become more complex and less intuitive. This part of the design process, called *verification*, becomes costly and error-prone, demanding the designer or verification engineer to do many long simulations and check the results against complex requirements.

This thesis is concerned with making the monitoring of simulations more efficient and reliable, as automatic as possible. It is centered around formalisms for specifying requirements, expected properties and performance measures that can be the basis for automatic monitoring, liberating the engineers from these tedious tasks. A large part of the thesis consists of novel theoretical and algorithmic contributions, related to formalisms based on temporal logic and regular expressions. These results are closer to the 'R' side of the R&D pipeline. The thesis also has a concrete applicative ingredient, namely, the implementation of such ideas in the context of existing industrial tools in the domain of electronic design automation (EDA) and more specifically for the design of analog and mixed-signal (AMS) circuits.

In general, *mixed-signal* verification of integrated circuits is an increasing source of challenges. This is due to the vastly different concerns, cultures, and modes of operation of digital and analog parts of the design and verification effort. As a result the amount of time spent on mixed-signal verification in a design project is becoming longer, with design errors escaping verification due to incompatible tools and approaches. To some extent, structured digital methodologies can be applied on mixed-signal circuits, by integrating analog verification results. However the further automation of mixed-signal verification, especially regarding mixed behaviors, requires novel ideas.

This thesis was conducted under the CIFRE framework in collaboration with Mentor Graphics, a leading software provider in EDA. In particular the work has taken place as part of the team in charge of developing Questa® ADMS<sup>™</sup>, a mixed-signal simulator. The collaboration gave invaluable insight into the domain, and also inspired several research directions.

### **Overview**

**Monitoring** The verification of systems by means of simulation involves the checking of each trace for correctness. In practice this monitoring activity can be entirely manual, proceeding by simple visual inspection of simulation traces in some waveform viewer. However for systems over a certain complexity, the verification effort always requires some automation. This can be achieved in one of several ways. For electronic circuits, dedicated *monitors* can be programmed as additional components. These monitors are integrated along with design blocks, or other verification components in the simulated testbench. In the case of analog monitors there are specific concerns of accuracy and repeatability, which we attempt to address. Another possibility is to use dedicated measurement and assertion languages. These high level languages are compiled separately into software monitors, that operate transparently along the simulation.

**Declarative Languages** Programming monitors that check simulation results can be a repetitive and error-prone task for designers and verification engineers. The use of declarative languages that are high-level and concise can help overcome such issues. Digital assertion languages enable using temporal logic and regular expressions, separately or in combination, to describe the system's sequential behavior. These assertions are compiled into procedural monitors by the simulation environment, and their violations are reported alongside other simulation results. In addition to automating the monitoring of properties, assertions enable further analysis such as marking the simulation trace for time intervals where some fault occurs. We provide extensions to the digital assertion framework towards the mixed-signal domain.

**Continuous-Time Properties** In the mixed-signal setting, we are primarily interested in the time-domain behavior of circuits. While in this regard digital circuits are mainly synchronous, analog circuits are mainly asynchronous. However after quantizing analog signals according to some thresholds, time-domain behaviors can usually be expressed as a combination of sequential behavior and timing constraints. The theory of real-time systems modeling and specification led to the development of specification languages based on temporal logic and regular expressions enhancing formal language theory with real-time aspects. Such extensions are praticularly relevant in our context. Real-time specifications do not however easily translate to effective, computational descriptions. We give algorithms for the monitoring of real-time specification languages.

**Quantitative Aspects** Some properties of systems called *specifications* are evaluated on a given simulation as being true or false, while other properties called *measures* yield real values. A measure can form a specification when asserted to lie in some range of values, as in "the average value of x is less than 2". Conversely a specification is turned into a measure by considering the distance from the given simulation trace to satisfying it, or violating it. This distance is also called the *robustness* of the simulation trace relative to the property. We give efficient algorithms for evaluating this distance, in the case of temporal logic specifications. In general the formalization of measures does not need to rely on strong theoretical notions, as digital assertions do with formal language theory.

Measurement languages are used routinely in analog circuits verification, and provide similar benefits to those obtained through the use of digital assertions. In a mixed-signal setting it makes sense to only measure some behavior over periods of time the circuit operates in some mode, that we in turn detect according to a sequence of events. We show how measures can be formalized this way, enabling further automation of mixed-signal verification.

**Interaction with Simulation** The monitoring process takes place either during simulation, we say *online*, or after the simulation, we say *offline*. Offline monitoring is done by storing all the signals associated with some variable appearing in the property under consideration. Having the option to process these signals moving back and forth in time, despite causing an overhead in memory consumption often simplifies treatment. Online monitoring offers a lot of possibilities in terms of interaction with the simulation. For instance a simulation may be stopped as soon as some assertion is violated, saving precious time for designers. Measurements performed in an online fashion can also take part in the stimulus generation process, improving the coverage or driving the design towards erroneous behavior. We give a framework to generalize the implementation of analog measurements into digital testbenches in an online fashion.

# Contributions

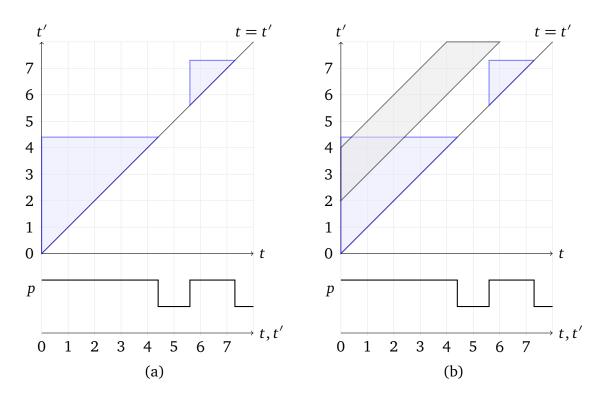

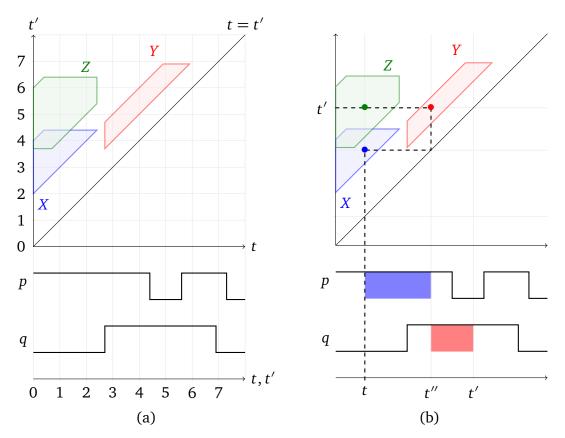

**Monitoring Timed Behaviors** Timed Regular Expressions (TRE) [25] are a convenient specification language for continuous-time behaviors. We extend the monitoring of continuous-time behaviors to specifications written using TRE. Our monitoring approach is similar in spirit to that of [83] for Metric Temporal Logic (MTL) [73]. While for temporal logic the domain to explore is the set of times at which the formula is satisfied, for regular expressions the domain to explore is the set of start time and end time pairs at which the expression is matched. We show that this set of time pairs can be decomposed into *zones*, simple convex sets used in timed systems formal verification. Results appear here as published in [110], but with additional focus on monitoring and integration with temporal logic. Additional results, namely the extension of this work to *online* monitoring, appear in [111].

**Robustness of Continuous Behaviors** The specification language Signal Temporal Logic (STL) [83], designed for mixed-signal behaviors, can be supplemented with a robustness indicator [53]. An important application of this robustness indicator is its use as a continuous variable that can be subject to optimization; this allows to detect bugs by varying simulation parameters towards minimizing the robustness value as in [67]. We develop new algorithms for the *robust monitoring* of Signal Temporal Logic (STL) based on a piecewise linear representation of signals. Among other results we use an algorithm described in [79] to guarantee a complexity comparable to that of the non-robust monitoring, and in particular linear in the length of the trace. This work was first exposed in [45] considering the case of (continuous) real signals; here we consider the more general case of traces with both Boolean and real signals.

#### INTRODUCTION

**Diagnostics of Timed Behaviors** Metric Temporal Logic has been the object of many theoretical investigations, and also had some applicative success with its extension to real signals STL. However the continuous-time interpretation of MTL is sometimes considered not intuitive by verification practitioners. To facilitate further adoption of MTL and its variants we investigate the diagnostics problem. The method that we propose makes it possible to debug a trace relative some specification, by finding a (minimal) set of segments of that trace sufficient to cause the violation of the specification. Solving this problem gives new insight into causality in continuous-time behaviors, with the notion of *temporal implicants*. This research also appears in [56]; it is presented here focusing on continuous-time traces, a characteristic specific to mixed-signal behaviors.

**Declarative Measurements** Measurements as defined in analog simulators provide a convenient way to extract performance indicators. For mixed-signal behaviors we found it advantageous to separate the measure itself from the description of time periods over which that measure takes place. We developed following this principle a declarative measurement language based on Signal Regular Expressions (SRE), an extension of TRE to real signals for this purpose, and basic continuous measures such as duration, minimum, or maximum of some signal. Our language is particularly applicable to mixed-signal simulations, for which measure time periods tend to be delimited by sequences of events corresponding discrete mode changes. This work initially appeared in [57], and is reproduced here using a simpler yet more expressive formalism.

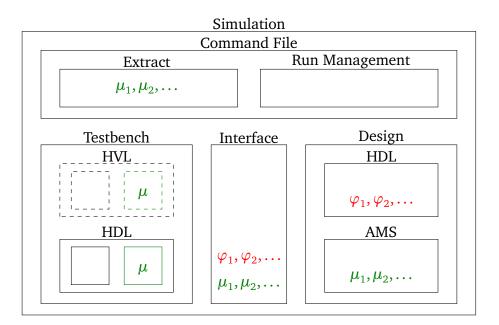

**Testbench Measurements** A notable difficulty in mixed-signal verification is that structured verification methodologies rely on a digital testbench, while measurements are performed using simulator command located elsewhere, in analog descriptions and simulation command files. We propose to make the functionality of these commands available in the form of system tasks, modules and classes in hardware description (or verification) languages, allowing to access the same algorithms. We use a uniform representation of input, output, and control signals in a measurement, and obtain the basis of a reusable library of measurement for mixed-signal verification.

## Organization

The thesis is organized as follows. Chapter 1 describes the context, motivation and state of the art in the mixed-signal verification domain. Chapters 2–3 lay down the foundations of our approach. In particular Chapter 2 demonstrates how discrete and continuous signals, sampling clocks, and timing checks can be integrated in the same assertion framework, while Chapter 3 exposes a monitoring algorithm for metric temporal logic that we later extend. Chapters 4–7 present research contributions, namely diagnosing metric temporal logic specifications and measuring their robustness, monitoring timed regular expressions and measuring continuous behaviors using such expressions. Readers who are not interested in the specific application domain can restrict themselves to these chapters while those interested primarily in AMS verification can read them lightly. Chapter 8 returns to the applicative domain and demonstrates how measurements defined by analog simulators can be brought into a digital testbench.

### Notation

We use the following notational conventions. Lower-case letters typically stand for numbers (a, b, ...) or functions (f, g, ...). Upper-case letters stand for sets (A, B, ...), and calligraphic letters stand for sets of sets  $(\mathscr{A}, \mathscr{B}, ...)$ . As customary we denote by  $\mathbb{N}$ , and  $\mathbb{R}$  the set of natural, and real numbers respectively. We extend this notation to denote sets  $(\mathbb{A}, \mathbb{B}, ...)$  that are fixed throughout a section or chapter.

The set of functions from *A* to *B* is denoted  $B^A$ . The powerset (set of subsets) of *A* is denoted  $2^A$  as usual. We denote by  $\cup \mathscr{A}$  the union of  $\mathscr{A}$ , with by definition  $\cup \mathscr{A} = \bigcup_{A \in \mathscr{A}} A$ . Truth values are represented using Boolean numbers 0 and 1. Functions from *A* to  $\{0, 1\}$ are called *predicates* over *A*. Predicates *P* over *A* are identified with subsets of *A*, so that we do not distinguish  $\{0, 1\}^A$  from  $2^A$ . By definition P(a) = 1 if and only if  $a \in P$  for any  $a \in A$ . Binary relations over *A* are identified with predicates over  $A^2 = A \times A$ , equivalently with subsets of  $A^2$ . For function *f* continuous at  $a \in \mathbb{R}$  we let  $f(a^+)$  and  $f(a^-)$  stand for the right-limit and left-limit of *f* at *a*, respectively.

A valuation is a mapping of variable symbols to some value domain. Variable symbols are lower-case letters (p, q, ...), and valuations are written using bold letters (u, v, ...). We denote  $q_v$  the value of variable q according to valuation v. Formal statements such as formulas and expressions are built from variable symbols and operators according to some grammar. We use Greek letters  $(\varphi, \psi, ...)$  to denote such formal statements and associated syntactic categories.

Algorithms are written in pseudo-code using lower-case letters for built-in routines, small capitals for user-defined routines, and bold letters for control flow instructions. We write mathematical symbols directly in pseudo-code when the implementation of the operation they denote is trivial or discussed elsewhere. Event-driven concurrent procedures are written using a syntax loosely based on Verilog, and their implementation discussed using Verilog constructs. This is purely conventional and does not intend to restrict the implementability to one particular language.

1

# **Mixed-Signal Verification**

In this chapter we present the applicative context of this thesis in Electronic Design Automation (EDA). The production of integrated circuits requires a particular phase that involves the use of *mixed-signal simulation*. The conjoint use of digital and analog models is in particular necessary to analyze the interaction between parts of the circuit implementing the two kinds of functionality. This enables modeling concisely Boolean and finite-state aspects in conjunction with some electrical effects. The simulation proceeds by synchronized execution of digital and analog simulators. Thus in a mixed-signal context all the usual analog and digital checks can performed; however the interaction of digital and analog parts creates the need for a specific verification effort. We briefly present assertions and measurements used in practice, and their limitations for the specification of mixed-signal behaviors.

## 1.1 Circuit Design

An increasing number of applications require a computerized system to interact with its physical environment in a non-trivial manner. Such cyber-physical systems [15] can be implemented on a single integrated circuit, what is known as a system on chip (SoC). The general trend is towards the integration of more functionality on a single integrated circuit. In the presence of both digital and analog functionality, we talk of *mixed-signal* circuit [75]. The design of digital or mixed signal integrated circuits<sup>1</sup> involves a simulation technique also dubbed *mixed-signal*.

The correct operation of an integrated circuit is usually verified by means of repeated simulations. During the specification phase the system is divided into large blocks, each implementing a particular function, and such that their composition implements all the desired functionality of the system. Blocks may be designed specifically for a given system, or reused from previous systems designed either by the same manufacturer or purchased from an external provider. In general, the process of creating an integrated circuit can be decomposed into the following phases: (1) specification; (2) design; (3) verification; (4)

<sup>&</sup>lt;sup>1</sup>Digital-intent circuits can also be considered as mixed-signal, when one takes into account the analog sub-circuits needed for their own operation, in particular for supplying power, or generating clock signals.

production; (5) testing. To some extent, the specification, design, and verification phases can be performed concurrently on all sub-systems. Such phases are then repeated on a larger system made of such blocks, see [60]. Verification of a sub-circuit relative to its environment typically ensures that its input-output relation conforms to some protocol or "contract", such as a range of operation for analog circuits.

Naturally, it is preferable to perform the verification as early as possible in the development process, and it has been shown that the cost of fixing an error increases exponentially with time [61]. When an error is only observed on the end product, fixing it requires identifying where the error occurred and applying again downstream phases after the error has been fixed. The methods we propose in this thesis can be applied for the early detection of errors in mixed-signal circuit designs.

### 1.2 Modeling

A circuit can be modeled in dedicated hardware description languages (HDL), or written in some other format specific to a analog simulators. These computerized descriptions are used for simulation, but also as input to other software tools for synthesis, place and route, etc. to generate the blueprint of the silicon chip itself. In the course of the complete design cycle of some integrated circuit, a given sub-circuit can have several models. Various *levels of abstractions* can be considered: real-number, behavioral, register transfer level, gate level, or electrical, to name but a few. The use of more than one abstraction enables considering necessary trade-offs between simulation speed and accuracy. Abstract models, ignoring some details or internal aspects of the circuit behavior, can be advantageous for the performance of the simulation. Their use is essential in simulating larger portions of a design. In this scenario, the aim is to explore the circuit behavior in sufficient detail to ensure that the practical realization will conform to the specifications.

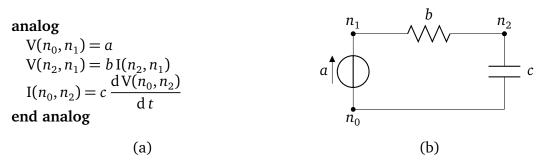

Hardware description languages such as Verilog [1] and VHDL [4] allow a representation of digital circuits close to that of concurrent computer programs. The state of the system is stored in some Boolean, integer, and floating-point variables. Such variables are updated via the traditional programming control structure with branching and looping constructs. An example of digital description appears Figure 1.1. In general, a digital description is decomposed into modules, which represent sub-circuits. Modules declare a list of ports, describing the interface, and procedural code, describing how port quantities and the internal state are updated based on events and deterministic delays. The procedural code has concurrent execution semantics. The synchronization of instructions is handled by events, which correspond to the change of state of some variable. A statement is executed on the occurrence of some event. It may in turn generate another event at a later time, according to some scheduling policy or some explicit delays.

The *de facto* standard for simulating analog circuits is known under the name of Simulation Program with Integrated Circuit Emphasis (SPICE) [92]. In this framework, the circuit description is that of a network of devices. The devices can be for example resistors, capacitors, or transistors. Their interconnection forms the circuit, and they are implicitly translated to differential equations for simulation. Alternatively the analog circuit equations can be given explicitly, using analog and mixed-signal modeling languages such as Verilog-AMS [9] and VHDL-AMS [2]. These languages enable decomposing the

```

always Q(p)

if s = 1 then s := 2

D

q

else if s = 2 then s := 1

q

end if

end always

1

0

q

always \mathbb{Q}(q)

if s = 0 then s := 1

else if s = 1 then s := 0

end if

end always

(a)

(b)

```

Figure 1.1: Finite Automaton: (a) Digital description; (b) Transition graph.

Figure 1.2: Linear electrical circuit: (a) AMS description; (b) Circuit schematic.

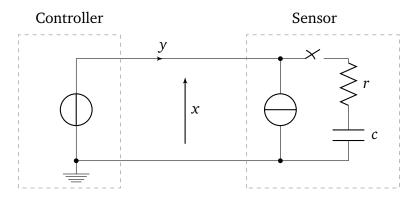

functionality in modules, similarly to digital description languages. Analog modules consist of a list of electrical ports, and procedural and equational analog statements. An example of an analog description appears in Figure 1.2. Equations describing the behavior of the model are collected across all analog statements. These languages also allow combining analog and digital statements, describing discrete and continuous dynamics conjointly in a mixed-signal model. Such models may naturally represent switched systems, continuous systems with discrete control; they may represent interface elements such as analog to digital, and digital to analog converters.

Digital descriptions can be split into two parts. One part belongs to the design under test (DUT), while the other part belongs to the *testbench*. In the DUT variables are static, they exist throughout the simulation. The testbench can be thought of as representing additional hardware blocks surrounding the DUT, or the software executing on the DUT. This later part of the code is used to generate stimuli, observe and process the response. Functionality in the testbench can be written using object oriented programming, in some hardware verification languages (HVL) such as SystemVerilog [7]. In addition to modules, testbench descriptions use constructs such as classes and interfaces. Variables in these parts of a testbench can be dynamic, created and deleted during simulation. Similar remarks can be made for analog descriptions. Part of the code, such as directed current or voltage source, or measurement functions, is not part of the design. These descriptions differ in that contrarily to the design they describe ideal behavior.

### 1.3 Simulation

A given DUT and environment featuring both digital and analog parts can be simulated in a software tool such as Mentor Graphics' Questa® ADMS<sup>TM</sup> [11]. Mixed-signal simulators are usually formed by assembling an event-driven simulator with an electrical circuit simulator [29]. Specific functionality enables splitting circuit descriptions between analog and digital parts, potentially creating additional components not present in the circuit description when some module is this way split. In simulation, digital and analog parts interact through *boundary elements*. These elements are inserted automatically at the interface between digital and analog parts. A digital to analog boundary element can be realized as a digitally controlled source (possibly with load); an analog to digital boundary element may be implemented as a quantizer (possibly with hysteresis).

The event-driven simulator compiles digital HDL instructions and executes the resulting program in a similar fashion to that for software environments. Additional features of hardware models are taken into account. The scheduling of events follows a standardized scheme as, for example, with Verilog [1]. Hardware descriptions allow for concurrent events, which can be executed in arbitrary order. This may create race conditions, in which the update of two quantities can happen in a non-deterministic order.

The electrical circuit simulator gathers equations from the given description, and provides a numerical solution up to the desired precision [93]. Such equations are derived from *devices*, and *connectivity*. Device equations are given explicitly in a model. Connectivity equations are determined according to Kirchhoff's current and voltage laws at each circuit node. The system of equations obtained is discretized according to a numerical integration scheme, such as Backward Euler, or Gear [59]. Discrete equations are solved at each time step via iterative methods such as Newton-Raphson.

A mixed-signal simulator alternates analog and digital *time steps*, in which analog and digital quantities are updated for after some given amount of time has elapsed. The size of digital time steps is determined by events scheduled according to the execution of digital modules, with fixed delays that are multiple of some time precision. The size of analog time steps depends on the numerical stability of the equations to solve, the estimated accuracy of the current solution, and user-provided thresholds for which the times of crossing need to be precisely detected. In particular, a different set of equations can be used when quantity x is below, and when it is above some threshold c, due to analog modeling or mixed-signal interaction. This can be indicated to the simulator using *threshold crossing* events, that we may denote  $\uparrow(x \ge c)$  for instance, whose effect is to force the simulator to make a step at the time where some quantity x crosses a predefined threshold c, here crossing it upward.

In this thesis we only consider *time-domain* properties; in a purely analog setting, other types of properties such as frequency-domain can be considered. The outcome of a time-domain simulation is a *trace* recording the evolution over time of digital and analog quantities of interest. Digital quantities are considered piecewise constant, following event-driven semantics. Analog quantities are considered piecewise polynomial. The interpolation scheme (naturally associated with the numerical integration scheme) may vary along the simulation – potentially requiring polynomials of degree more than one. However more samples can be added to the trace in order to ensure that in offline analysis, linear interpolation is always sufficient.

### 1.4 Verification

The verification of mixed-signal circuits often proceeds with purely digital and purely analog verification methods, based on what type of property is observed. Let us first introduce the verification practice in each separate domain, and then discuss mixed-signal verification specifically.

#### 1.4.1 Digital

Simulation-based (dynamic) verification and formal (static) verification of digital circuits are well-established in industrial practice [76]. Formal verification of digital circuits was initially based on theorem proving [33], and now mostly relies on *model checking* [35]. In the model checking activity, the system model is checked against some formal statement or property, also called an *assertion*. Formal methods are limited in application to (critical) sub-circuits with manageable size, the mainstream approach to verification remains simulation-based. Like formal verification, simulation-based verification can make use of formal property languages. The objective here is to check that all simulations conform to the specification. The use of formal property languages in the perspective of checking simulations is known as *assertion-based verification*.

In order to ensure that most or all aspects of the circuit's functionality are exercised in simulation, the generation of stimuli to the circuit can be based on coverage indicators. We talk in that case of *coverage-driven verification*, and the use of randomization in that perspective leads to the notion of *constrained-random* simulation. Due to the time investment needed to develop this kind of testbench, it should be as reusable as possible. For this one may use object-oriented programming constructs. Combining all such techniques can be done using the Universal Verification Methodology (UVM), developed in collaboration between the major electronic design automation suppliers [8]. This effort resulted in a set of SystemVerilog classes to easily implement verification techniques in a digital testbench.

Checking that the DUT reacts correctly to the given stimuli can be done by implementing *monitors* directly as modules in HDL or classes in HVL. An orthogonal approach is to use assertions [39]. In hardware design, an assertion is a piece of code specifying a sequential property, ranging across several clock cycles. The two principal assertion languages for digital circuit design are called SystemVerilog Assertions (SVA) [1] and Property Specification Language (PSL) [6]. The former is integrated in the hardware description language SystemVerilog, while the latter may be used together with any hardware description language, according to simulator support.

#### 1.4.2 Analog

Analog verification proceeds by repeated simulations under varying parameter values, with the aim of exhibiting the quality of a single behavior. This can take several forms, with a so-called *corners* simulation exploring extreme values, Monte Carlo simulation using randomized values, or more elaborate scenarios using intermediate simulations results to guide the choice of parameters. This practice dominates the verification of small analog blocks and tends to be less present for larger blocks or at system level.

Analog verification usually features a first phase, in which meaningful quantities are extracted, according to the circuit intent. We talk of measurements, by analogy with physical measurements taking place during the testing phase – here we mean virtual measurements, applied to simulated values. The quantities extracted from the simulation include period, slew rate, duty cycle, and rise time. Generic functions such as integral, maximum, can also be used for that purpose. Measured values can be checked against bounds, or composed into more elaborate indicators. Measurement commands reside in the run management file, or may directly feature in a SPICE netlist.

Once a meaningful quantity has been extracted, the verification primarily consists in checking that it is within the correct range, also called Safe Operating Area (SOA). The notion of SOA initially applied to the analysis of voltages and currents at transistors ports, and by extension it applies to the analysis of arbitrary quantities measured in the context of a simulation. Analog simulators allow the designer to check such safety properties automatically, via dedicated commands. Such specifications can handle conditional statements based on arithmetic expressions and comparison operators, and timing relaxation in which the unsafe area may be entered for a specified maximum amount of time.

#### 1.4.3 Mixed-Signal

Mixed-signal functionality may relate the time-domain behavior of digital signals and analog signals. This is the case for analog-to-digital or digital-to-analog converter circuits. There are established techniques to specify and evaluate the performance of this particular class of circuits. Digital signals may have lower rate of change than analog, when they act as control for the analog part. In other situations analog signals may be the ones with a lower rate of change. In such cases one part may be approximated as constant, and the verification is then repeated over many modes, or parameter values. In that sense, outside of converters, in mixed-signal circuits the temporal interaction of analog and digital signals is relatively rare.

The verification of a mixed-signal design is said to be *analog-centric*, or *digital-centric* depending on the principal intent of the design. The verification of analog circuits is less structured, and in analog-centric verification mixed-signal does not require a special treatment. On the other hand, digital circuits typically undergo a structured verification process. Support for verifying analog functionality in a digital-centric environment is crucial to the relevance of digital techniques. Some steps have been done in that direction in some commercial simulators:

- SOA violations reported alongside digital assertions and counted in coverage;

- analog quantities can be used in expressions within digital assertions;

- libraries of analog probes and sources are available in AMS languages.

With analog extensions of hardware design languages such as Verilog-AMS, it is also possible to extend the digital practice towards incorporating analog features. For example [115] and [30] propose analog monitors implemented in this fashion. A major difficulty with implementing an analog and mixed-signal testbench is that while HDLs have mixed-signal capabilities, this is not the case of major HVLs such as SystemVerilog. A current effort from software providers is the merging of Verilog-AMS with SystemVerilog. This will facilitate the access of analog quantities from within a digital testbench, and may be a first step towards a general purpose mixed-signal description and verification language [82].

### **1.5** Measurements

The role of measurements is to process simulation traces in order to extract relevant quantities, or *measures*. Such measures can be obtained by taking a maximum, an average value, or computing delays and slopes of signals in a variety of ways. Analog verification heavily relies on measurements; typically the verification is a two-layer process that extracts some measures, and checks that they are within the expected range. Measurements can be written in dedicated languages such as the MEAS library initially implemented by Synopsys [3], and EXTRACT library implemented by Mentor Graphics [10]. These libraries provide statements that can appear in SPICE descriptions, or alongside the run-management part of a simulation.

In the context of measurements, a signal can be seen either as a discrete-time sequence of values, or as a continuous-time piecewise-linear / piecewise-constant function of time. In general, we may define a measurement as a mapping from signals to signals. This covers the case of continuous-time signals via interpolation, discrete-time signals, and single values seen as sequences of length one. The time component of a measure is usually defined as the instant at which the measure was extracted.

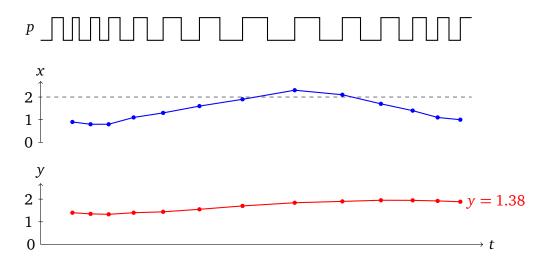

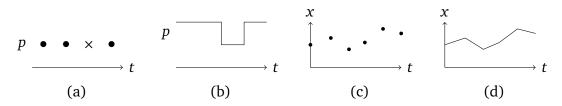

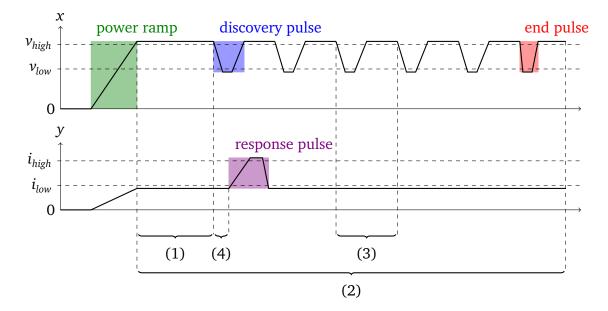

**Example 1.1.** Consider the measurement y = average(period(p)), illustrated in Figure 1.3. The period is simply defined as the amount of time elapsed between consecutive rising edges of p. This measure can be taken several times over a signal p featuring more than two rising edges. The computation of y = average(x) involves representing x as a set of discrete values, and produces another set of discrete values; typically only the last one would be of interest. We may also want to check that the period of p does not go above value 2 for too long, for which we would interpret signal x as continuous and could use interpolation.

Some measurements are restricted to time periods during which the system is in a certain state. In many situations, entering or leaving a some state can be detected by simple trigger and target events, such as some signal crossing a given threshold. Measurements of this kind can be specified by the MEAS library. In other situations, the measurement can be specified using an absolute time window, for instance when a particular stimulus is applied, and the behavior is expected to occur within a fixed time window. Measurements of that kind are easily described using the EXTRACT library.

#### 1.6 Assertions

Digital assertions enable specifying sequential behaviors. They can be written in dedicated languages PSL and SVA, which feature two main layers: (1) regular expressions, and (2) temporal logic. The regular expression layer is used to describe sequences of events, in order to detect that the design enters a given state. The temporal logic layer

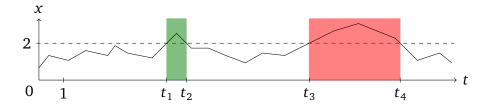

Figure 1.3: Extracting measure x = period(p), checking x against threshold 2, and extracting y = average(period(p)) in turn.

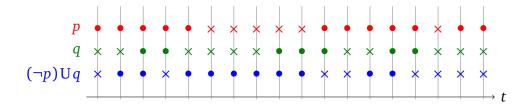

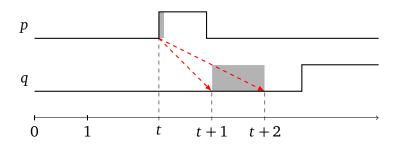

is used to describe invariants using operator *always* denoted  $\Box$ , and reactive properties based on such sequences, using suffix implication denoted  $\hookrightarrow$ . Typical assertions are of the form  $\Box \varphi$ , with  $\varphi = \rho_1 \leftrightarrow \rho_2$  given  $\rho_1$  and  $\rho_2$  some regular expressions. Such an expression reads " $\rho_1$  is always followed by  $\rho_2$ ", and its meaning is as follows: any segment of the trace that matches  $\rho_1$  is immediately followed by another segment that matches  $\rho_2$ .

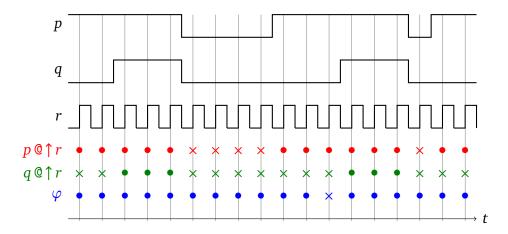

Digital circuits are synchronized by clocks, and assertions are often evaluated under the associated sampling. The sampling may be implicit, or may apply to some assertion  $\varphi$  in the from of some event  $\uparrow r$ , with the assertion written  $\varphi @\uparrow r$ . Properties of interest sometimes involve more than one clock, typically when describing the interaction between parts of the circuit driven by different clocks. One may specify such properties using multi-clock assertions, which feature a regular expression or temporal logic statement split between two sampling clocks. For example, one can specify a sequence of events ( $\rho_1 @\uparrow r_1$ )  $\cdot$  ( $\rho_2 @\uparrow r_1$ ) that describes a segment of the trace matching  $\rho_1$  with sampling given by  $\uparrow r_1$  and followed by another segment matching  $\rho_2$  with sampling given by  $\uparrow r_2$ .

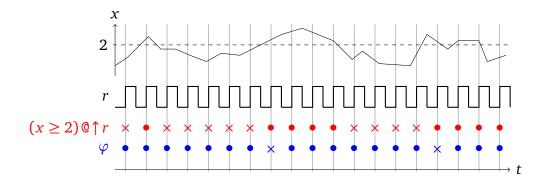

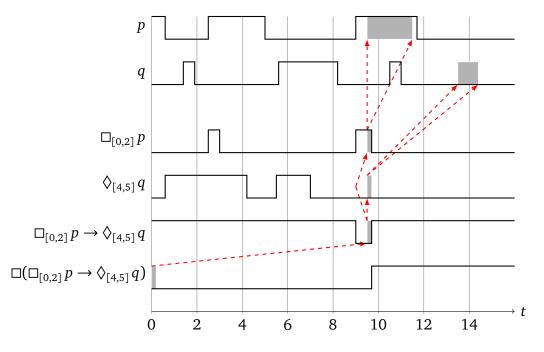

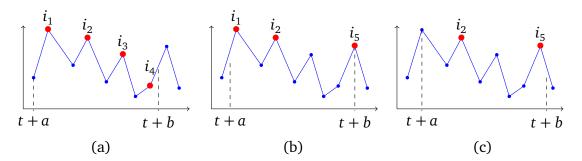

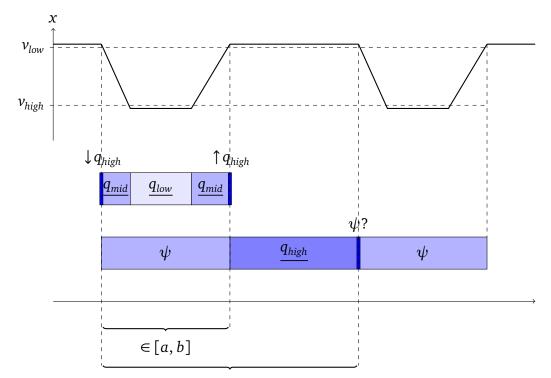

**Example 1.2.** Consider the property  $\varphi = (p \cdot p \cdot p \cdot p \circ p \circ \neg p \cdot \neg p) @\uparrow r$ . It uses for sampling the rising edges of signal r. Based on this sampling it requires that each sequence of four consecutive occurrences of p should be followed either by an occurrence of q or two consecutive occurrences of  $\neg p$ . The monitoring of this assertion on a given simulation trace is illustrated in Figure 1.4.

Analog assertions can be formed in one of two ways. The first way to specify analog behaviors is to use CHECKSOA instructions, dedicated to checking the safe operation of electrical circuits. Such statements allow to check if some simulated or measured quantity stays within some range (safe area), and in a more general way, for how long does it leave the designated range. This is particularly suited for checking correctness of some analog behavior of the circuit, focusing on the stable values (discarding short spikes). Safe operating area checks can also include preconditions in the form of arbitrary

Figure 1.4: Evaluation of concurrent assertion  $\varphi = (p \cdot p \cdot p \to p \to q \lor \neg p \cdot \neg p) @\uparrow r$  on a given simulation trace.

Figure 1.5: Checking safe operating area of x using a continuous time representation. A spike above 2 is safe if it lasts less than 3 time units (in green), but is unsafe when it lasts 3 time units or longer (in red).

propositional formulas over propositions of the form  $x \le c$  or x < c for some measured quantity x and threshold c. Outside timing relaxation, automated safe operating area checks do not support the specification of sequential behaviors.

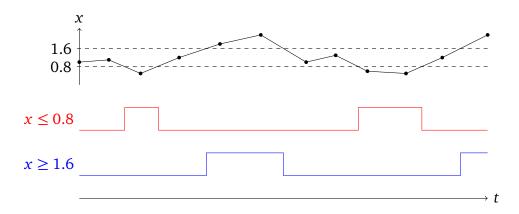

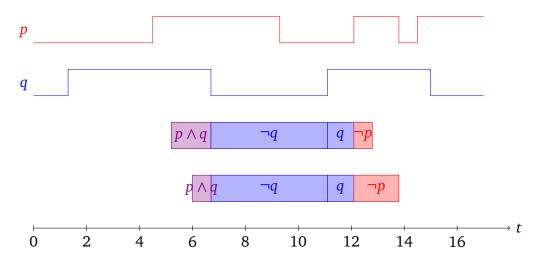

**Example 1.3.** Consider the property according to which that signal x either stays less than 2, or does not stay above threshold 2 for more than 3 time units; see Figure 1.5 for an illustration. Signal x can be a primitive quantity simulated in the circuit such as the voltage at some node, or a measured quantity such as the period of some signal, as in Figure 1.3.

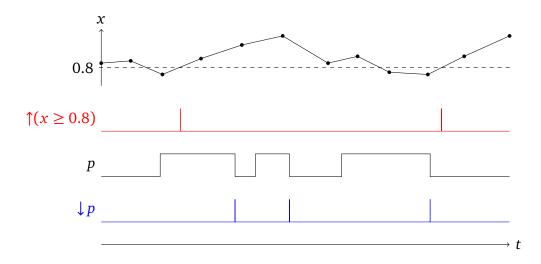

The second way to specify analog behaviors is to use digital assertion languages over analog quantities. Unlike safe operating area checks, digital assertions can specify sequential behaviors. Continuous signals can be incorporated into the regular and temporal layers of digital assertions via two mechanisms. The first mechanism consists in replacing digital variables  $p, q, \ldots$  by threshold propositions over analog variables  $x > 1, y \le 2, \ldots$ and using a digital sampling clock. One drawback is that glitches occurring between sampling points are ignored. This phenomenon is exemplified in Figure 1.6. The second mechanism consists in replacing the digital sampling event  $\uparrow r, \downarrow s, \ldots$  by some analog event such as  $\uparrow(x > 1), \downarrow(y \le 2), \ldots$  and using simple true or false conditions. A difficulty associated with this solution is that the sampling cannot be used to measure the elapsed time, as with a periodic digital sampling clock. There one may resort to storing

Figure 1.6: Checking safe operating area of *x* using a discrete time approximation  $\varphi = (\neg (p \cdot p \cdot p)) @\uparrow r$ . The specification appears violated at the end of the trace (four consecutive sampled values of *x* above 2) whereas it is marginally satisfied (*x* does not stay above 2 for more than 2 time units).

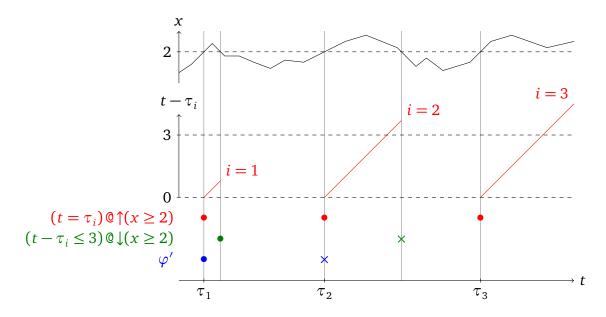

Figure 1.7: Checking safe operating area of *x* using analog events, local variable based assertion  $\varphi' = \forall \tau (\tau = t) @\uparrow (x \ge 2) \Leftrightarrow (t - \tau \le 3) @\downarrow (x \ge 2)$ . The last event marking the exit of *x* from safe area is not matched by an event marking its return, so that the violation goes undetected.

the absolute time of events via a local variable, and computing delays by subtracting such times. The drawback of using this encoding is that the presence of some analog event cannot be asserted unless one uses the notion of *strong* and *weak* expressions as standardized in [113], which are not implemented in all commercial simulators. The default semantics is that of weak expressions, according to which the absence of clock ticks will not cause the assertion to fail as illustrated Figure 1.7. Here the clock tick is defined as the occurrence of some analog event.

# 2

# Specifying Discrete and Continuous Properties

This chapter introduces a framework for the specification of mixed-signal behaviors, obtained by extending standard hardware assertion languages towards continuous behaviors. A system design features several variables representing quantities and their evolution in time. Not all quantities are defined at all times; we consider two models of time: discrete (a finite set) and continuous (a dense interval of the reals). The monitoring process computes additional quantities of particular interest on a given simulation: propositions, events, properties, and measures. We then introduce declarative property languages of temporal logic and regular expressions; along with *suffix implication* are the backbone of hardware assertion languages. For digital behaviors, assertions feature a sampling event, based on some clock signal. We redefine the semantics of sampling operators as changing the underlying temporal domain. For analog and mixed-signal behaviors, we introduce formalisms featuring real-time constraints, along with continuous checks. Our definitions can form the basis of an integrated mixed-signal assertion language.

#### 2.1 Introduction

The specification of mixed properties, involving both digital and analog behaviors, is still an active research topic. Not all mixed-signal circuits exhibit such behaviors. Often, the behavior of the circuit can be split between analog and digital parts, which do not interact in a dynamic fashion. Yet the verification of mixed-signal interaction still remains a bottleneck in the design of integrated circuits. A unified language for specifying analog and digital behaviors would have the advantage of concepts reuse. In particular it is possible to use the same operators to specify sequential aspects, those of regular expressions and temporal logic. However as seen, the nature of the temporal domain in digital and analog circuits is fundamentally different. In the case of digital behaviors, correct timing consists in a range of clock cycles. In the case of analog behavior, correct timing consists in a range of delay values. Sampling with a digital clock of fixed period, the number of clock cycles also stands for a time delay. Yet the specificity of analog behaviors however is that events arrive in an asynchronous manner. Thus using a periodic sampling clock on analog signals results in reduced accuracy. Continuous time specification languages, as with Metric Temporal Logic (MTL) [73] and Timed Regular Expressions (TRE) [25], do not suffer from this limitation, as they treat time as a real value. Another important aspect of analog behaviors is that the state of some analog circuit cannot always be taken as some signal value. The state of some analog circuit is better represented by some measure applied to continuous signals produced by the circuit. We can also add time domain measurements to our framework. Such measurements can easily be integrated to assertions by considering the values it produces as forming another signal produced by the simulation.