# UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : **informatique**Arrêté ministérial : 7 août 2006

Présentée par

# Pranav TENDULKAR

Thèse dirigée par **Oded Maler** et codirigée par **Peter Poplavko**

préparée au sein du laboratoire Verimag et de Ecole Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# Mapping and Scheduling on Multicore Processors using SMT Solvers

Thèse soutenue publiquement le **13th October 2014**, devant le jury composé de :

**Dr. Albert Cohen**

INRIA, Paris, Rapporteur

**Prof. Marc Geilen**

Technical University of Eindhoven, Netherlands, Rapporteur

**Prof. Dimitrios S. Nikolopoulos**

Queen's University, Belfast, UK, Examinateur

Dr. Alain Girault

INRIA, Grenoble, Examinateur

Dr. Benoît Dinechin

Kalray, Examinateur

**Dr. Phil Harris**

United Technologies Research Center, Cork, Ireland, Examinateur

Dr. Oded Maler

CNRS, Verimag, Directeur de thèse

Dr. Peter Poplavko

Verimag, Co-Directeur de thèse

# ACKNOWLEDGEMENTS

Foremost I would like immensely thank Oded Maler who is my thesis supervisor, but much more. He persistently helped me throughout my PhD. and provided motivation, research directions to carry out my work. But more importantly he gave me unparalleled freedom to explore my varied interests while choosing a topic for my thesis. He made me understand research and many other things in general and broader sense. He has been a continuous source of inspiration and motivation, to carry out the work, especially in times when things were obscure. He always provided me more than enough time and guidance where it was utmost necessary and ensured that I remained focussed on my topic. It was a privilege to work at Verimag especially with Oded, since he always provided a healthy and relaxed work atmosphere. He always blended humor with our daily chores at Verimag which teared down undesired tensions and frustrations. I had a great time at Grenoble working under his supervision. He was like a friend when we met over many lunches or dinners, with his entertaining and knowledgeable discussions on diverse topics. I will forever cherish the time that we shared during these years.

I am deeply thankful to Peter Poplavko who inspired me to work on dataflow models. Although according to Oded, he *hijacked* me to this domain. Peter played a very important role in my thesis. He was providing me a continuous feedback on my work. He enabled me to understand how to persistently attack a problem. He was actively guiding me throughout all my PhD. I thank him for all our discussions, code reviews, publication writing exercises etc. in which he invested a lot of his time. Especially the feedback on my thesis even when he was on vacation was of great help. I am confident that I would never have been able to complete this thesis without him.

I would like to thank the jury members and the reviewers for attending my thesis defense. I especially thank them for their valuable feedback on the manuscript. The feedback gave me an additional perspective to my own work. I am very happy to have such a jury.

I also want to thank the group at Technical University of Eindhoven who supported me for an internship. It was a very different and wonderful experience to work there. Prof. Sander Stuijk and his team were immensely supportive during my work. A few names I would like to mention are Hamid Reza Pourshaghaghi, Francesco Comaschi, Sebastian Moreno, Rosilde Corvino, Karthik Chandrasekar. Out of my office I made many friends in Eindhoven who accompanied me in several evenings for dinner, playing cards, skating and many other things. I will always remember the time that I spent with Deepak Jain, Srivathsa Bhat, Sushil Shirsath, Sandip Pawar, Aroa Izquierdo and many others.

I want to thank all my colleagues in Verimag. Sophie Quinton, Irini-Eleftheria Mens, Abhinav Srivastav, Alexios Lekidis and many of them. We always crack jokes on PhD. life and make fun of our situations which seemed to be going nowhere. I believe I had a great working environment, sharing my views, talks, presentation etc. with my friends. I would like to convey my thanks to the administrative staff which was a life-line for me in France. I still remember my struggles as a non-french speaking foreigner and without their help I would have been nowhere.

A special thanks goes to Dorit Maler. I enjoyed the time that we spent with her in informal meetings. We shared such memorable discussions, that I would cherish for rest of my life. I

still remember how confident I felt after I talked with her just before my defense. She is a wonderful person, and I feel lucky to know her closely.

Finally, I want to thank most supportive and loveable parents, who have been there for me always, irrespective of all the things. I am indebted to them to the last bit for being there and bringing the best out of me. Along with them, I thank my sisters and extended family for their support even if I am far away for a long time. I want to thank my wife "Vrushali", for her constant support in good and bad times. She accompanied me without any complain irrespective of my negligence towards her. I am grateful to have such companion. I dedicate this thesis to my parents and my wife.

# ABSTRACT

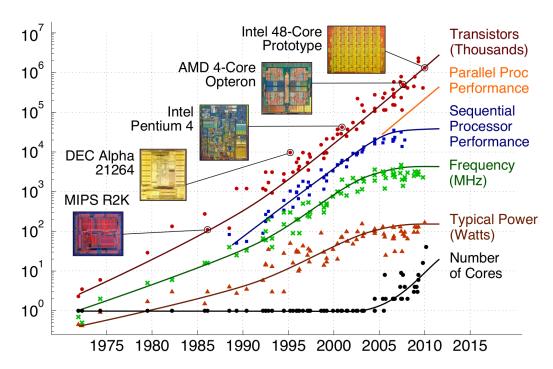

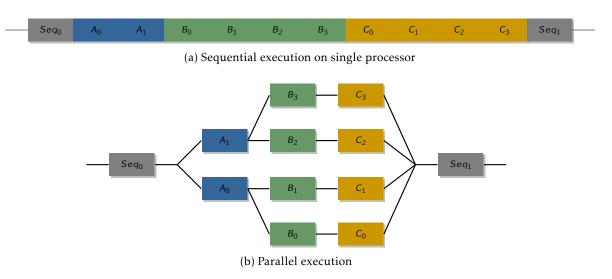

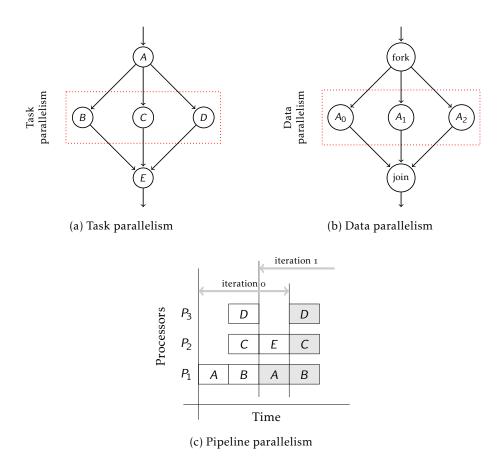

In order to achieve performance gains in the software, computers have evolved to multi-core and many-core platforms abounding with multiple processor cores. However the problem of finding efficient ways to execute parallel software on these platform is hard. With a large number of processor cores available, the software must orchestrate the communication, synchronization along with the execution of the code. Communication corresponds to the transport of data between different processors, which either can be handled transparently by the hardware or explicitly managed by the software. Synchronization is a requirement of proper selection of start time of computations e.g. the condition for software tasks to begin execution only after all its dependencies are satisfied.

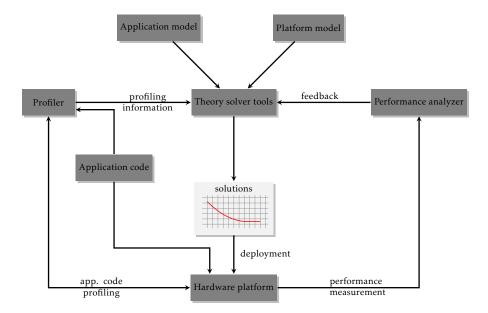

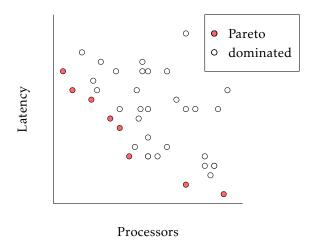

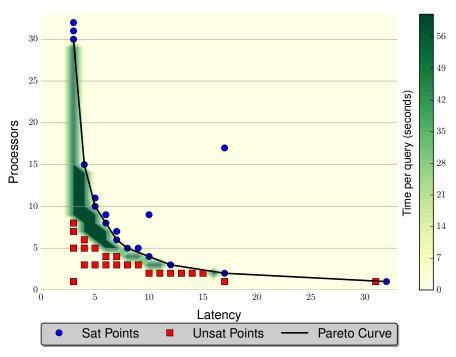

Models which represent the algorithms in a structured and formal way expose the available parallelism. Deployment of the software algorithms represented by such models needs a specification of which processor to execute the tasks on (*mapping*) and when to execute them (*scheduling*). Mapping and scheduling is a hard combinatorial problem to solve with a huge design space containing exponential number of solutions. In addition, the solutions are evaluated according to different costs that need to be optimized, such as memory consumption, time to execute, static power consumption, resources used etc. Such a problem with multiple costs is called a *multi-criteria* optimization problem. The solution to this problem is not a unique single solution, but a set of incomparable solutions called *Pareto* solutions. In order to track multi-criteria problems, special algorithms are needed which can approximate the Pareto solutions in the design space.

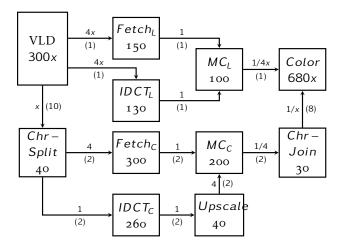

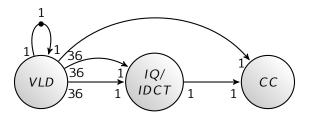

In this thesis we target a class of applications called *streaming* applications, which process a continuous stream of data. These applications typically apply similar computation on different data items. A common class of models called *dataflow* models conveniently expresses such applications. In this thesis, we deal with mapping and scheduling of dataflow applications on many-core platforms. We encode this problem in form of logical constraints and present it to *satisfiability modulo theory* (SMT) solvers. SMT solvers, solve the encoded problem by using a combination of search techniques and constraint propagation to find an assignment to the problem variables satisfying the given cost constraints.

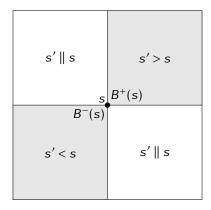

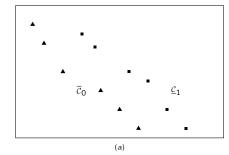

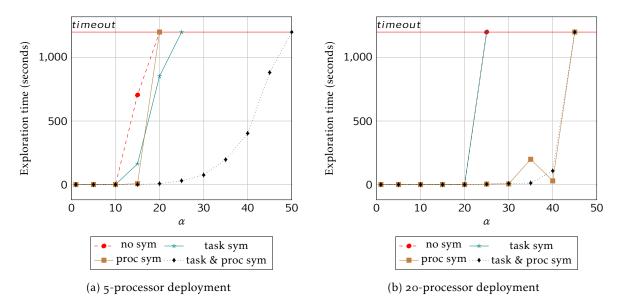

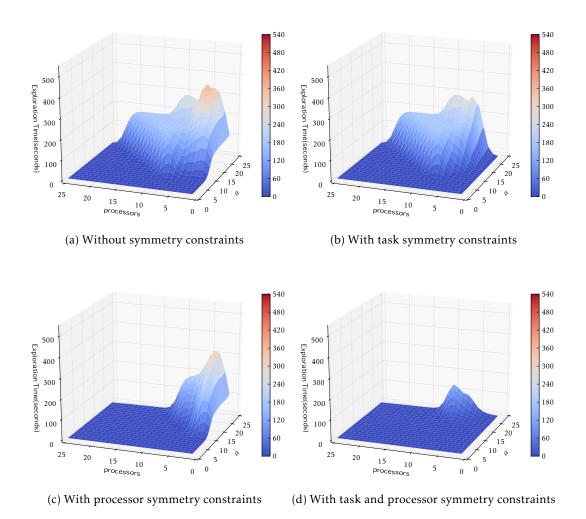

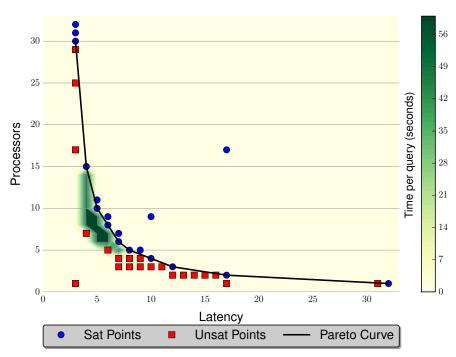

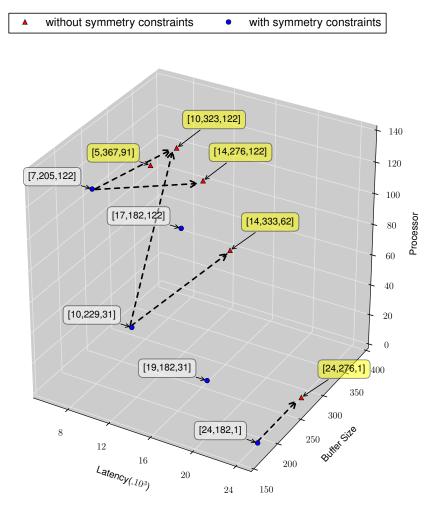

In dataflow applications, the design space explodes with increased number of tasks and processors. In this thesis, we tackle this problem by introducing symmetry reduction techniques and demonstrate that symmetry breaking accelerates search in SMT solvers, increasing the size of the problem that can be solved. Our design-space exploration algorithm approximates the Pareto front of the problem and produces solutions with different cost trade-offs. We validate these solutions by executing them on a real multi-core platform.

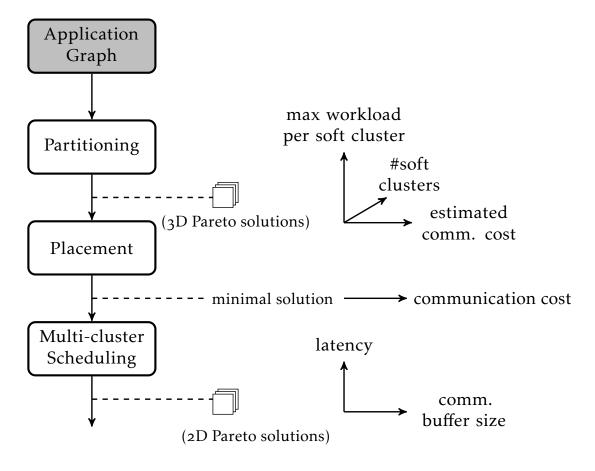

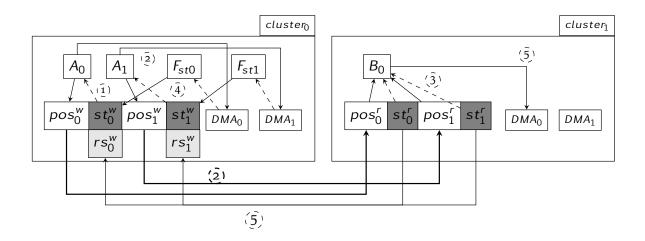

Further we extend the scheduling problem to the many-core platforms which are assembled from multi-core clusters connected by network-on-chip. We provide a design flow which performs mapping of the applications on such platforms and automatic insertion of additional elements to model the communication. We demonstrate how communication with bounded memory can be performed by correctly modeling the flow-control. We provide experimental results obtained on the 256-processor Kalray MPPA-256 platform.

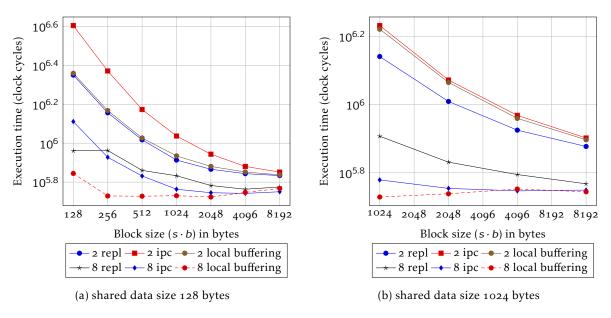

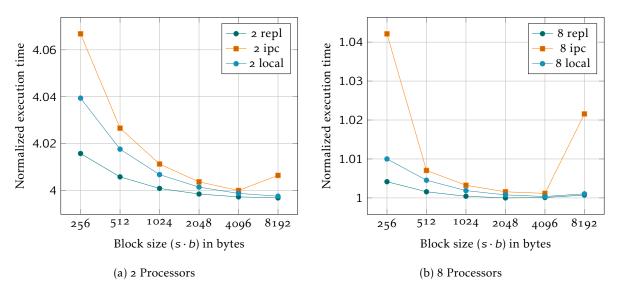

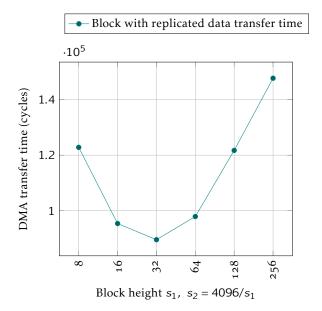

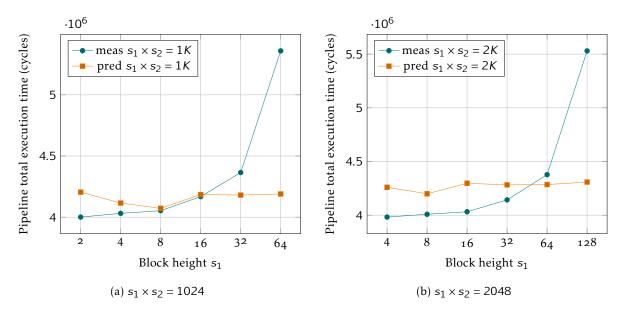

iv abstract

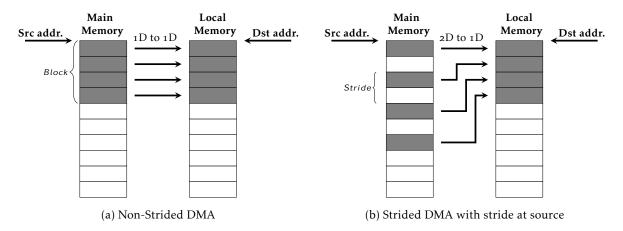

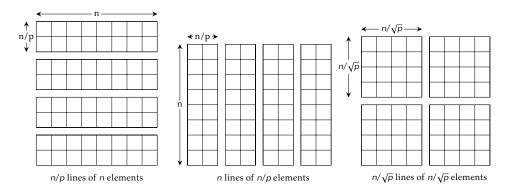

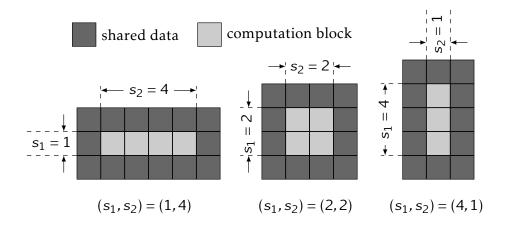

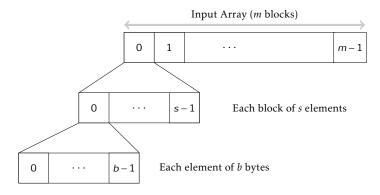

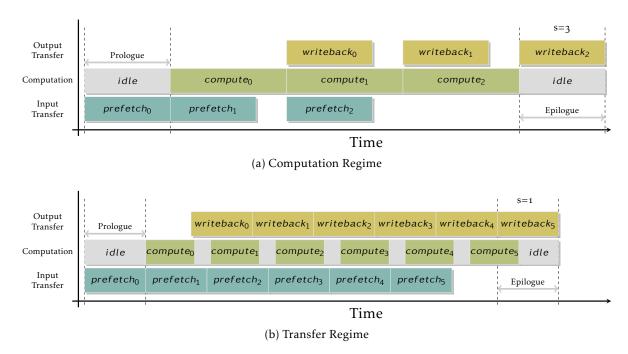

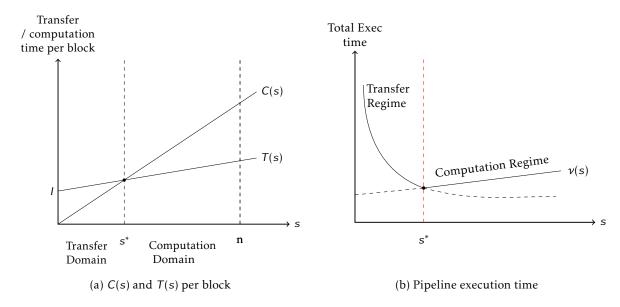

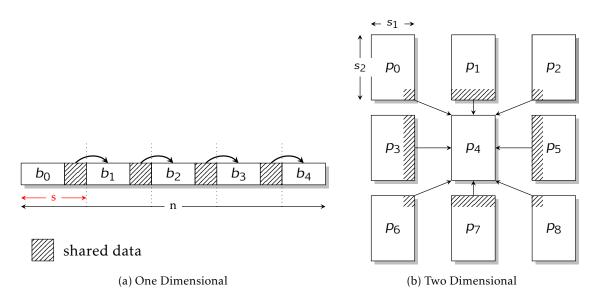

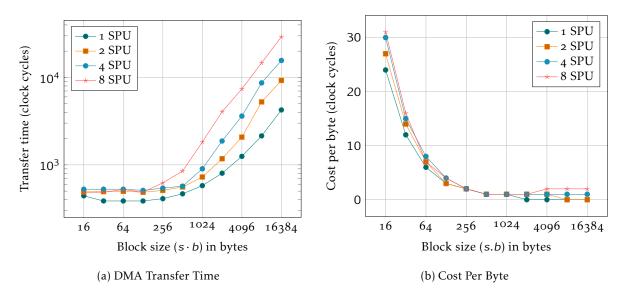

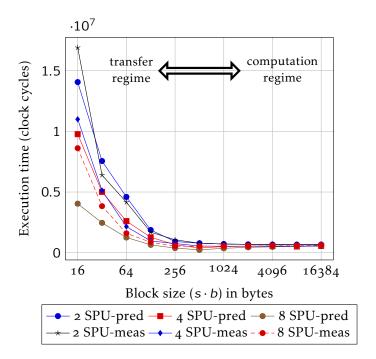

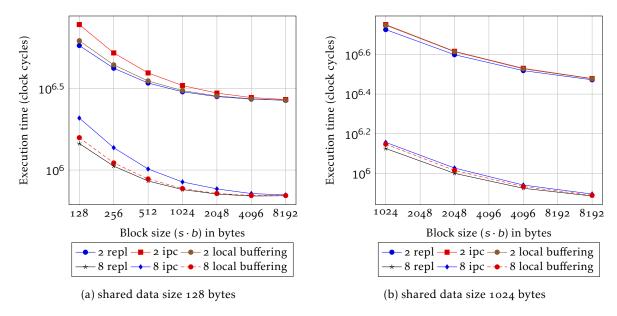

Multi-core processors have typically a small amount of memory close to the processor. Generally application data does not fit in the local memory. We study a class of parallel applications having a regular data access pattern, with large amount of data to be processed by a uniform computation. Such applications are commonly found in image processing. The data must be brought from main memory to local memory, processed and then the results written back to main memory, all in batches. Selecting the proper granularity of the data that is brought into local memory is an optimization problem. We formalize this problem and provide a way to determine the optimal transfer granularity depending on the characteristics of application and the hardware platform. Further we provide a technique to analyze different data exchange mechanisms for the case where some data is shared between different computations.

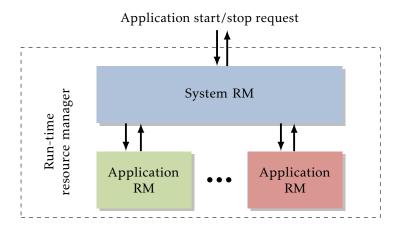

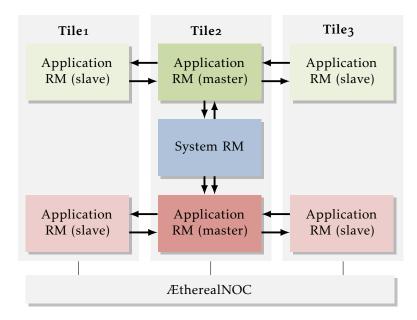

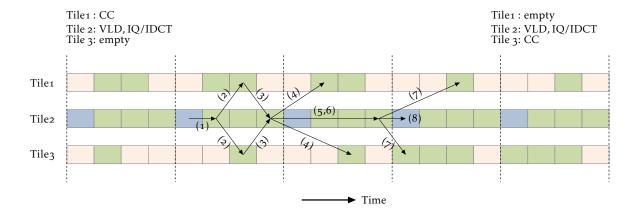

Applications in modern embedded systems can start and stop dynamically. In order to execute all these applications efficiently and to optimize global costs such as power consumption, execution time etc., the applications must be reconfigured at runtime. We present a predictable and composable way (executing independently without affecting others) of migrating tasks according to the reconfiguration decision.

Keywords: Multi-core, many-core, dataflow, mapping, scheduling, SMT solver

# Résumé

Dans l'objectif d'augmenter les performances, l'architecture des processeurs a évolué vers des plate-formes "multi-core" et "many-core" composées de multiple unités de traitements. Toutefois, trouver des moyens efficaces pour exécuter du logiciel parallèle reste un problème difficile. Avec un grand nombre d'unités de calcul disponibles, le logiciel doit orchestrer la communication et assurer la synchronisation lors de l'exécution du code. La communication (transport des données entre les différents processeurs) est gérée de façon transparente par le matériel ou explicitement par le logiciel.

Les modèles qui représentent les algorithmes de façon structurée et formelle mettent en évidence leur parallélisme inhérent. Le déploiement des logiciels représentés par ces modèles nécessite de spécifier placement (sur quel processeur s'exécute une certaine tâche) et l'ordonnancement (dans quel ordre sont exécutées les tâches). Le placement et l'ordonnancement sont des problèmes combinatoires difficile avec un nombre exponentiel de solutions. En outre, les solutions ont différents coûts qui doivent être optimisés : la consommation de mémoire, le temps d'exécution, les ressources utilisées, etc. C'est un problème d'optimisation multi-critères. La solution à ce problème est ce qu'on appelle un ensemble Pareto-optimal nécessitant des algorithmes spéciaux pour l'approximer.

Nous ciblons une classe d'applications, appelées applications de streaming, qui traitent un flux continu de données. Ces applications qui appliquent un calcul similaire sur différents éléments de données successifs, peuvent être commodément exprimées par une classe de modèles appelés modèles de flux de données. Le problème du placement et de l'ordonnancement est codé sous forme de contraintes logiques et résolu par un solveur Satisfaisabilité Modulo Théories (SMT). Les solveurs SMT résolvent le problème en combinant des techniques de recherche et de la propagation de contraintes afin d'attribuer des valeurs aux variables du problème satisfaisant les contraintes de coût données.

Dans les applications de flux de données, l'espace de conception explose avec l'augmentation du nombre de tâches et de processeurs. Dans cette thèse, nous nous attaquons à ce problème par l'introduction des techniques de réduction de symétrie et démontrons que la rupture de symétrie accélère la recherche dans un solveur SMT, permettant ainsi l'augmentation de la taille du problème qui peut être résolu. Notre algorithme d'exploration de l'espace de conception approxime le front de Pareto du problème et produit des solutions pour différents compromis de coûts. De plus, nous étendons le problème d'ordonnancement pour les plate-formes "many-core" qui sont une catégorie de plate-forme multi coeurs où les unités sont connectés par un réseau sur puce (NoC). Nous fournissons un flot de conception qui réalise le placement des applications sur de telles plate-formes et insert automatiquement des éléments supplémentaires pour modéliser la communication à l'aide de mémoires de taille bornée. Nous présentons des résultats expérimentaux obtenus sur deux plate-formes existantes : la machine Kalray à 256 processeurs et les Tilera TILE-64.

Les processeurs multi-coeurs ont typiquement une faible quantité de mémoire proche du processeur. Celle ci est généralement insuffisante pour contenir toutes les données necessaires au calcul d'une tâche. Nous étudions une classe d'applications parallèles présentant un patvi résumé

tern régulier d'accès aux données et une grande quantité de données à traiter par un calcul uniforme. Les données doivent être acheminées depuis la mémoire principale vers la mémoire locale, traitées, puis, les résultats retournés en mémoire centrale, tout en lots. Fixer la bonne granularité des données acheminées en mémoire locale est un problème d'optimisation. Nous formalisons ce problème et proposons un moyen de déterminer la granularité de transfert optimale en fonction des caractéristiques de l'application et de la plate-forme matérielle.

En plus des problèmes d'ordonnancement et de gestion de la mémoire locale, nous étudions une partie du problème de la gestion de l'exécution des applications. Dans les systèmes embarqués modernes, les applications peuvent démarrer et s'arrêter dynamiquement. Afin d'exécuter toutes les applications de manière efficace et d'optimiser les coûts globaux tels que la consommation d'énergie, temps d'exécution, etc., les applications nécessitent d'être reconfigurées dynamiquement à l'exécution. Nous présentons une manière prévisible et composable (exécution indépendamment sans affecter les autres) de réaliser la migration des tâches conformément à la décision de reconfiguration.

# Contents

| A  | BSTRA | ACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | iii |  |  |  |  |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| Ré | SUM   | É                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V   |  |  |  |  |

| 1  | Int   | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |  |  |  |  |

|    | 1.1   | Multi-core Processor System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   |  |  |  |  |

|    |       | 1.1.1 Host Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3   |  |  |  |  |

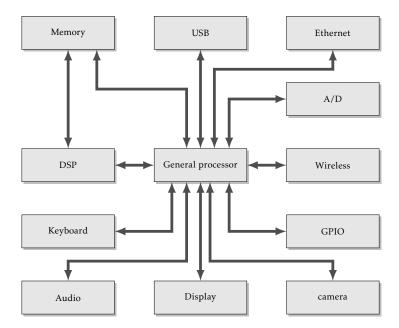

|    |       | 1.1.2 Peripheral Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3   |  |  |  |  |

|    |       | 1.1.3 Multi-core Fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4   |  |  |  |  |

|    |       | 1.1.4 Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5   |  |  |  |  |

|    |       | 1.1.5 Network Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5   |  |  |  |  |

|    | 1.2   | Multi-core Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6   |  |  |  |  |

|    |       | 1.2.1 Theoretical issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6   |  |  |  |  |

|    |       | 1.2.2 Practical Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10  |  |  |  |  |

|    | 1.3   | Software Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10  |  |  |  |  |

|    | 1.4   | Related Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11  |  |  |  |  |

|    |       | 1.4.1 SDF <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11  |  |  |  |  |

|    |       | 1.4.2 MAMPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11  |  |  |  |  |

|    |       | 1.4.3 MP-Opt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11  |  |  |  |  |

|    |       | 1.4.4 StreamIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11  |  |  |  |  |

|    |       | 1.4.5 StreamRoller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11  |  |  |  |  |

|    |       | 1.4.6 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12  |  |  |  |  |

|    | 1.5   | Organization of Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12  |  |  |  |  |

| 2  | Pro   | GRAMMING MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15  |  |  |  |  |

|    | 2.1   | Dataflow graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |  |  |  |  |

|    |       | 2.1.1 Static Dataflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |  |  |

|    |       | 2.1.2 Dynamic Dataflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17  |  |  |  |  |

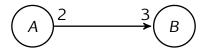

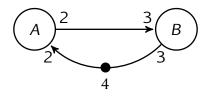

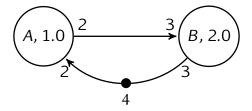

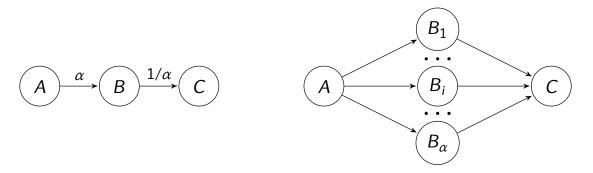

|    | 2.2   | Synchronous Dataflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |  |  |  |  |

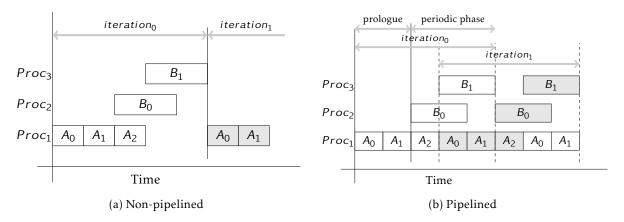

|    | 2.3   | Split-Join Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20  |  |  |  |  |

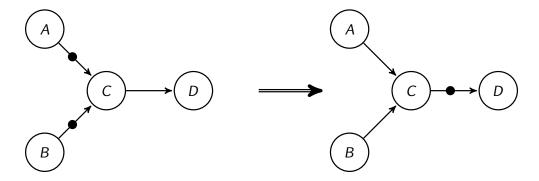

|    |       | 2.3.1 The Semantics of Split-join Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21  |  |  |  |  |

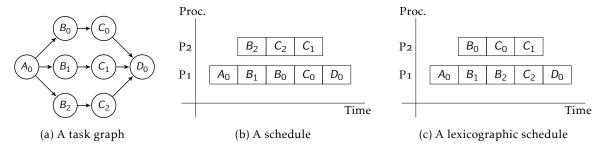

|    |       | 2.3.2 Derived Task Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22  |  |  |  |  |

|    |       | 2.3.3 Marked Split-join Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22  |  |  |  |  |

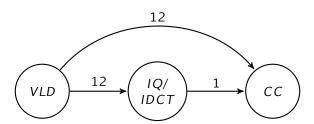

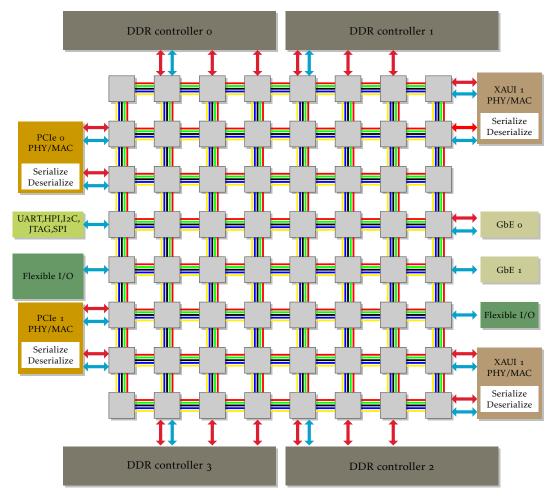

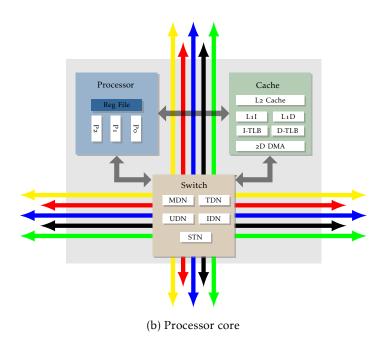

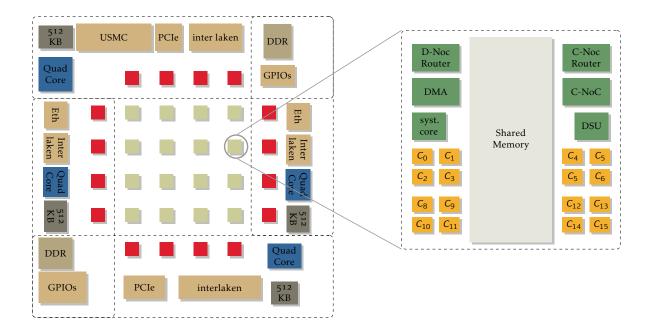

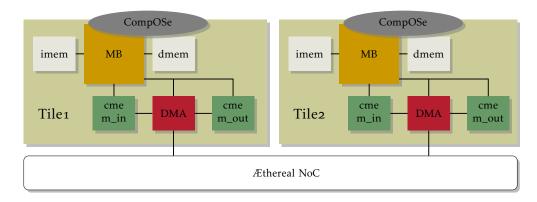

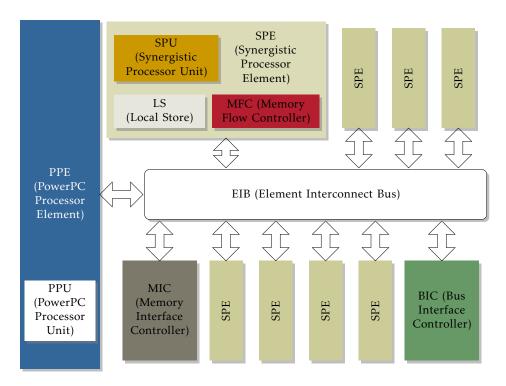

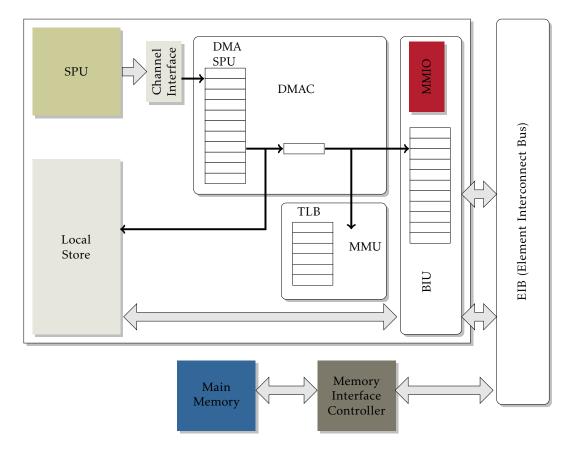

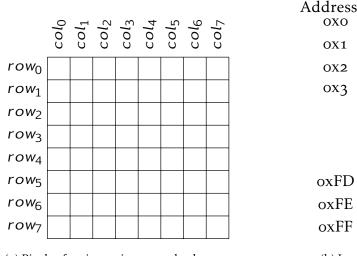

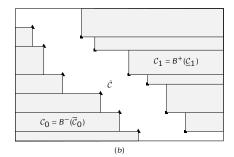

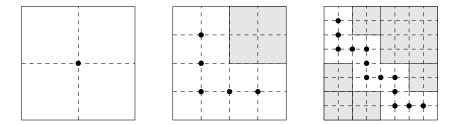

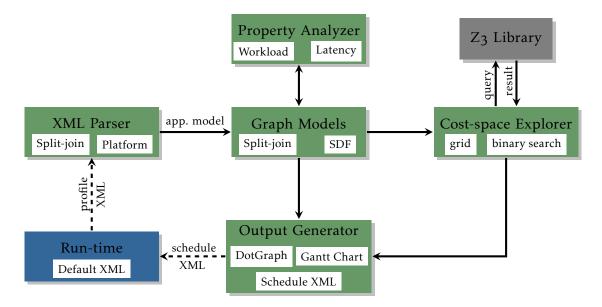

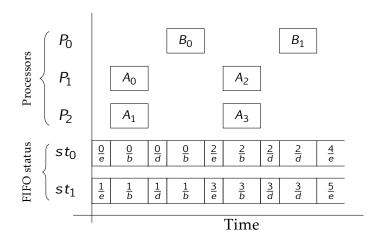

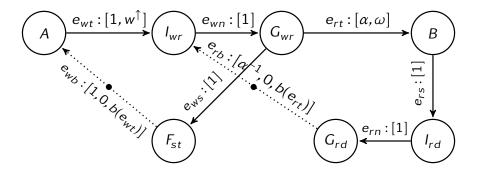

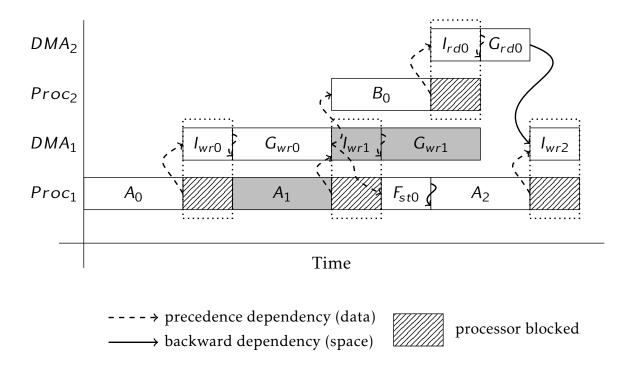

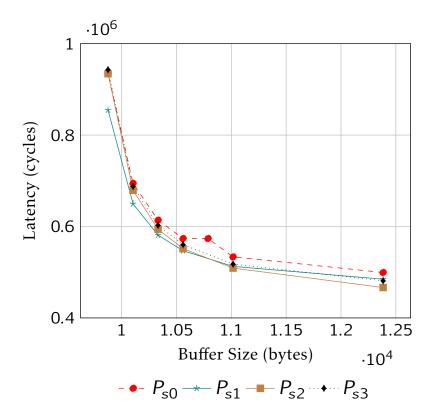

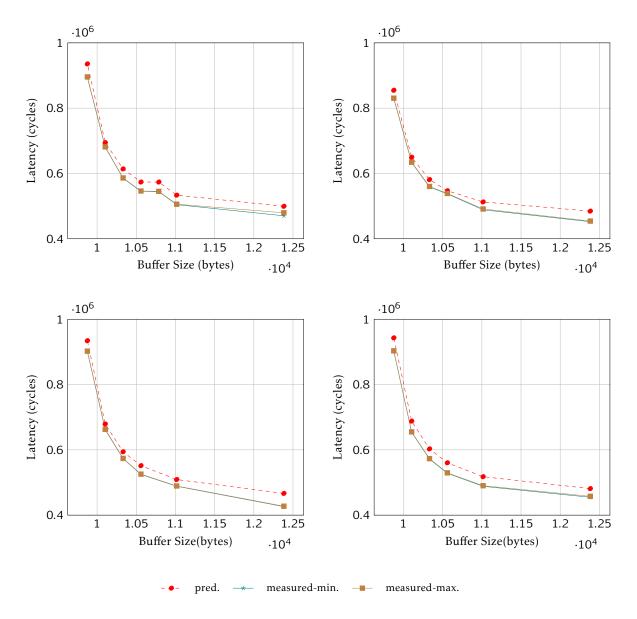

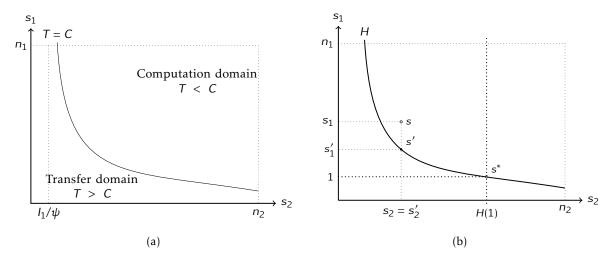

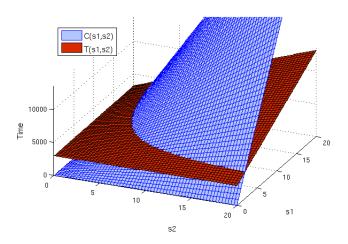

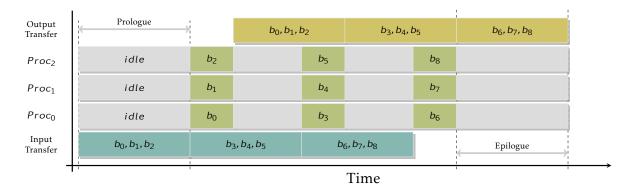

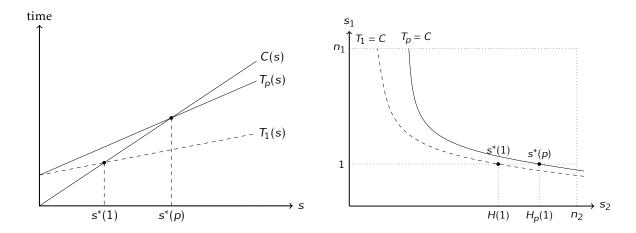

|    | 2.4   | a transfer and a transfer at the second seco |     |  |  |  |  |