#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| N° | att | ribu | ué | par | la | bił | olic | othe | èque | e |

|----|-----|------|----|-----|----|-----|------|------|------|---|

|    |     |      |    |     |    |     |      |      |      |   |

#### THESE

### pour obtenir le grade de DOCTEUR DE L'INP GRENOBLE Spécialité: Micro et Nano Electronique

Préparée au laboratoire VERIMAG

dans le cadre de l'Ecole Doctorale Electronique, Electrotechnique, Automatique & Traitement du Signal

présentée et soutenue publiquement

par

#### **Ramzi BEN SALAH**

le 12 octobre 2007

## SUR L'ANALYSE TEMPORISÉE DE SYSTÈMES DE GRANDE TAILLE

#### JURY

| Mme. Florence Maraninchi | : Président          |

|--------------------------|----------------------|

| M. Amir Pnueli           | : Rapporteur         |

| M. Ahmed Bouajjani       | : Rapporteur         |

| M. Edmund M. Clarke      | : Examinateur        |

| M. Klaus Winkelmann      | : Examinateur        |

| M. Ziyad Hanna           | : Examinateur        |

| M. Oded Maler            | : Directeur de thèse |

| M. Marius Bozga          | : Co-encadreur       |

|                          |                      |

## ON TIMING ANALYSIS OF LARGE SYSTEMS

by Ramzi BEN SALAH 12 October 2007 "I think the right way, of course, is to say that what we have to look at is the whole structural interconnection of the thing; that all the sciences, and not just the sciences but all the efforts of intellectual kinds."

[Richard Feynman]

## Abstract

This thesis is part of an effort to advance the algorithmic analysis of timed systems from a proofof-concept phase toward industrial usage, by improving the performance of timing verification algorithms. Models and tools based on timed automata can be used for timing and performance analysis of complex systems, hardware and software alike, but the problem of scalability prevents the adaptation of these techniques by industry.

The two major contributions of the thesis are an improved algorithm for symbolic reachability computation which reduces significantly the state exposition, and a compositional divide-and-conquer methodology based on conservative approximation of timed components.

With standard reachability computation, a discrete state reached by different orderings of the same set of transitions, will lead often to different symbolic states, contributing to additional state explosion. We provide an algorithm which avoids this problem, taking advantage of the fact that the union of all the zones of these symbolic states is convex and hence they can be merged into one zone. This algorithm has been implemented and tested experimentally.

The second contribution of this thesis benefits from the modularity of component based systems to build for each component a model which approximates its timed interface behavior. These models could be reused for the modeling of the interface of component reusing this last component. Thus the modeling process is done hierarchically starting from the leaves and abstracting at each level the internal complexity of every component, focusing only on their external behavior which is sufficient for their reuse.

Two abstraction techniques are developed in the thesis, one specialized for systems that have to respond to a finite number of events, and one more general for systems working in arbitrary general environment. Both techniques are based on introducing auxiliary input-related clocks, performing reachability computation and then projecting the timing constraints of the obtained automaton on the auxiliary clocks. As a result we obtain an automaton with fewer clocks whose quantitative semantics is an over-approximation but its qualitative semantics is exact. Further steps of hiding and minimization lead to a small automaton for the component.

# Acknowledgments

I was very fortunate to work under the supervision of Oded Maler, which has combined together guidance, advice, encouragement and support. I thank him for his confidence in me, which allowed me to benefit fully from this experience. I learned a lot from working with him, from his optimism and his positive attitude.

I also had an enormous pleasure to work with Marius Bozga. I thank him for the time he has devoted to our fruitful discussions. I would like to use this opportunity express my great respect for his professional and human qualities.

I want to thank the members of the jury: Prof. Florence Maranninchi, of the National Polytechnic Institute of Grenoble for chairing the jury, Prof. Amir Pnueli of New York University and Prof. Ahmed Bouajjani of Paris 7 University for the interest they have given to this work; Prof. Edmund Clarke of Carnegie Mellon University of Pittsburgh, and Mr. Klaus Winkelmann of OneSpin Solution in Munich/Germany, for the honor they gave me by participating in my jury.

In Verimag I have had the opportunity to grow and interact with some of the most talented and accomplished researchers in the field. In particular I had the privilege to interact with Paul Caspi, Eugene Asarin, Stavros Tripakis and Sergio Yovine. Thanks for their advices.

I also want to thank Goran Frehse, Dejan Nickovic and Viktor Schuppan for the effort they have invested reading and commenting my thesis. Thanks for the rest of the members of Verimag who were able to create the ideal atmosphere and working conditions.

Thanks to Ananda, Olivier and Hung for these evenings of exotic cuisines. Thanks to all my friends inside and outside the laboratory that made my stay in Grenoble a real human experience.

Finally, a big thank for my family, who despite the distance, were able to find a way to support me. But thinking of my family, my brothers and sisters, I cannot forget other people whose friendship is the better gift that these years gave me; Sometimes words cannot convey what we want to express.

# Contents

| 1 | Intr | oduction                                                     | 1  |

|---|------|--------------------------------------------------------------|----|

|   | 1.1  | Formal Verification                                          | 1  |

|   | 1.2  | Timed Systems                                                | 4  |

|   | 1.3  | Thesis Framework                                             | 8  |

| Ι | Tin  | ned Automata and Interleaving                                | 11 |

| 2 | Tim  | ed Automata                                                  | 13 |

|   | 2.1  | Timed Automata through an Example                            | 13 |

|   | 2.2  | Preliminary Definitions                                      | 17 |

|   |      | 2.2.1 Clocks, Time Constraints and Zones                     | 17 |

|   |      | 2.2.2 Timed Automata Syntax and Semantics                    | 20 |

|   | 2.3  | Symbolic Reachability                                        | 24 |

|   |      | 2.3.1 From Timed Automata to Reachability Graphs             | 25 |

|   |      | 2.3.2 From Reachability Graphs to Interpreted Timed Automata | 28 |

| 3 | On ] | Interleaving in Timed Automata                               | 31 |

|   | 3.1  | Introduction                                                 | 31 |

|   | 3.2  | Zone Explosion due to Interleaving                           | 32 |

|   | 3.3  | Convexity Result                                             | 34 |

|   | 3.4  | Application to Reachability Computation                      | 39 |

|   | 3.5  | Experimental Results                                         | 41 |

|   | 3.6  | Related Work                                                 | 45 |

| II | Va                                           | riables Based Timed Automata and Component Based Systems         | 47 |  |  |  |  |

|----|----------------------------------------------|------------------------------------------------------------------|----|--|--|--|--|

| 4  | Timed Automata with Discrete State Variables |                                                                  |    |  |  |  |  |

|    | 4.1                                          | Variables, Valuations and Assignments                            | 50 |  |  |  |  |

|    | 4.2                                          | Signals                                                          | 51 |  |  |  |  |

|    | 4.3                                          | Timed Automata with Variables                                    | 55 |  |  |  |  |

| 5  | Tin                                          | ed Circuits                                                      | 61 |  |  |  |  |

|    | 5.1                                          | Circuit Timing                                                   | 62 |  |  |  |  |

|    | 5.2                                          | Circuit Structure                                                | 66 |  |  |  |  |

|    | 5.3                                          | Delays in Digital Circuits                                       | 68 |  |  |  |  |

|    | 5.4                                          | Circuit Model                                                    | 70 |  |  |  |  |

|    | 5.5                                          | Analysis                                                         | 71 |  |  |  |  |

| 6  | Abs                                          | raction: Acyclic Environments                                    | 77 |  |  |  |  |

|    | 6.1                                          | Acyclic Input Generators                                         | 77 |  |  |  |  |

|    | 6.2                                          | The Abstraction Technique                                        | 78 |  |  |  |  |

|    |                                              | 6.2.1 Summary                                                    | 78 |  |  |  |  |

|    |                                              | 6.2.2 Interpreted Timed Automata with an Additional Global Clock | 80 |  |  |  |  |

|    |                                              | 6.2.3 Projection on Global Time                                  | 80 |  |  |  |  |

|    |                                              | 6.2.4 Projection on Output Variables                             | 82 |  |  |  |  |

|    |                                              | 6.2.5 Minimization                                               | 84 |  |  |  |  |

|    | 6.3                                          | Applications                                                     | 88 |  |  |  |  |

|    |                                              | 6.3.1 A Divide and Conquer Analysis Algorithm                    | 88 |  |  |  |  |

|    |                                              | 6.3.2 Experimental Results                                       | 91 |  |  |  |  |

|    | 6.4                                          | Summary                                                          | 91 |  |  |  |  |

| 7  | Abs                                          | raction: General Environments                                    | 95 |  |  |  |  |

|    | 7.1                                          | Introduction                                                     | 95 |  |  |  |  |

|    |                                              | 7.1.1 Motivation                                                 | 95 |  |  |  |  |

|     | 7.1.2  | An Overview of the Abstraction Procedure       | 97  |

|-----|--------|------------------------------------------------|-----|

| 7.2 | Addin  | g Input Clocks                                 | 98  |

|     | 7.2.1  | Life and Death of Events                       | 98  |

|     | 7.2.2  | From $\mathcal{A}$ to $\mathcal{A}^{+\hat{C}}$ | 99  |

| 7.3 | Reach  | ability, Projection and Minimization           | 103 |

|     | 7.3.1  | Reachability Computation                       | 103 |

|     | 7.3.2  | Clock Projection                               | 103 |

|     | 7.3.3  | Variable Projection and Minimization           | 104 |

| 7.4 | Conclu | usions                                         | 105 |

|     |        |                                                |     |

### III Achievements and Conclusions

111

| 8 | TCA  | CA: Timed Circuits Analyzer Toolbox |     |  |  |  |  |

|---|------|-------------------------------------|-----|--|--|--|--|

|   | 8.1  | Introduction                        | 113 |  |  |  |  |

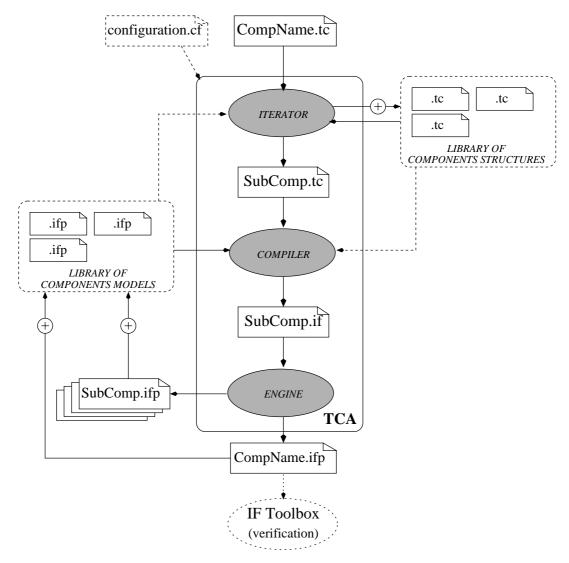

|   | 8.2  | Global View of the TCA Tool         | 113 |  |  |  |  |

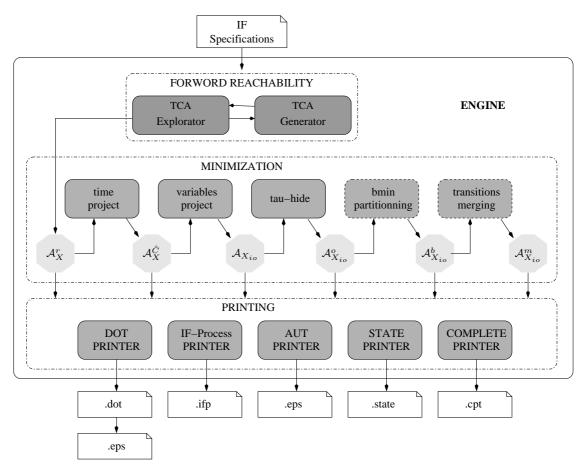

|   | 8.3  | Deeper View of the TCA Tool         | 116 |  |  |  |  |

|   |      | 8.3.1 The ITERATOR                  | 116 |  |  |  |  |

|   |      | 8.3.2 The COMPILER                  | 118 |  |  |  |  |

|   |      | 8.3.3 The ENGINE                    | 118 |  |  |  |  |

|   | 8.4  | Conclusion                          | 122 |  |  |  |  |

| 9 | Cone | onclusions and Future Work 1        |     |  |  |  |  |

|   | 9.1  | Summary                             | 123 |  |  |  |  |

|   | 9.2  | Future Work                         | 124 |  |  |  |  |

# **List of Figures**

| 1.1 | Model Checking.                                                           | 4  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Refining a discrete transition into a process that takes time             | 6  |

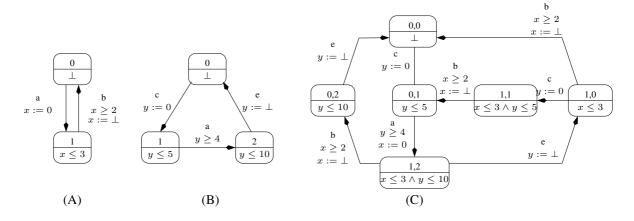

| 2.1 | An example of timed automaton                                             | 15 |

| 2.2 | Operations on timed zones                                                 | 19 |

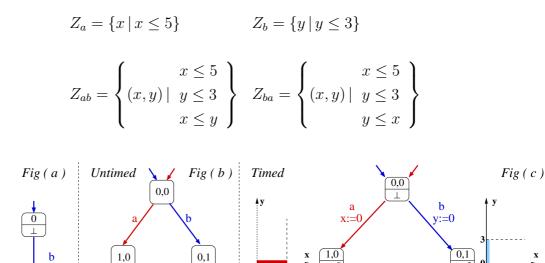

| 2.3 | Product of Timed Automata                                                 | 23 |

| 2.4 | The reachability graph of the timed automaton of Figure 2.1               | 28 |

| 2.5 | Interpreted timed automaton of the timed automaton of Figure 2.1          | 29 |

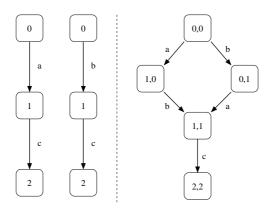

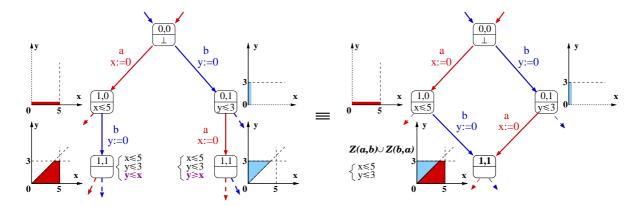

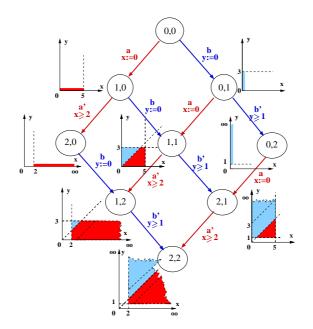

| 3.1 | Composing automata with independent actions                               | 32 |

| 3.2 | Interleaving in timed automata                                            | 33 |

| 3.3 | Semantics preserving reduction on a small example                         | 34 |

| 3.4 | The part of a component which participates in a global run                | 37 |

| 3.5 | A product of two timed automata.                                          | 41 |

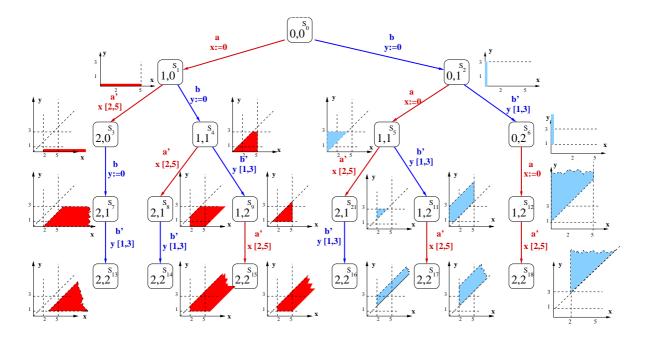

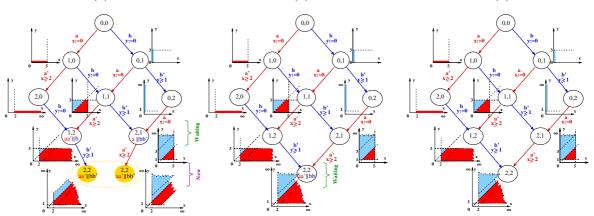

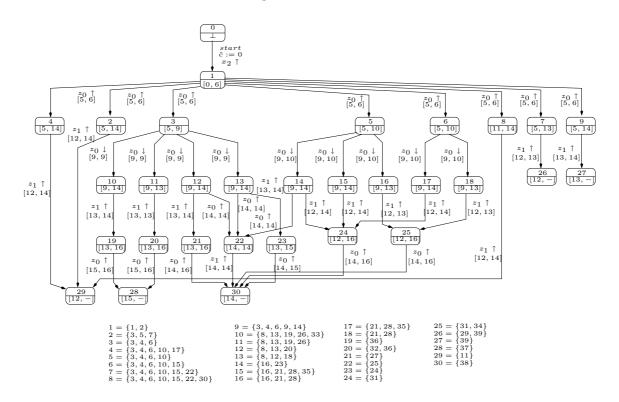

| 3.6 | The standard reachability graph for the automata of Figure 3.5            | 42 |

| 3.7 | A reduced reachability graph for the system of Figure 3.5                 | 42 |

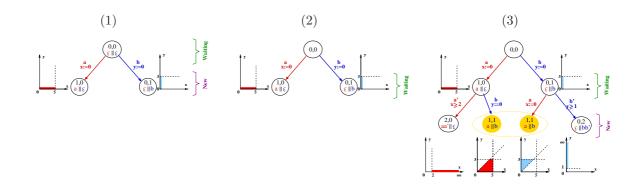

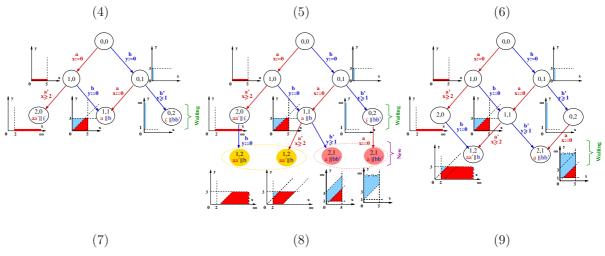

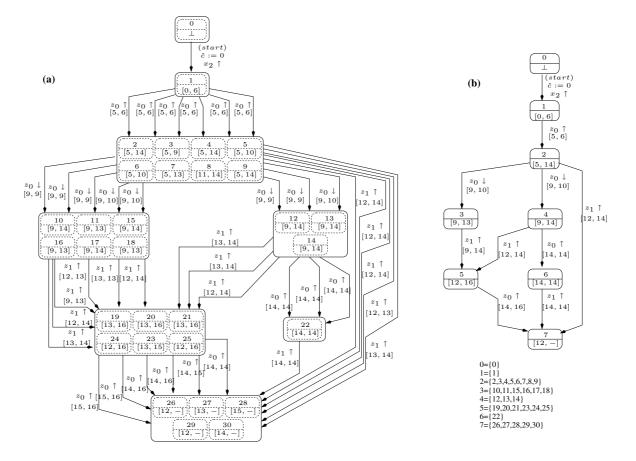

| 3.8 | The operation of the introduced algorithm                                 | 43 |

| 3.9 | The structure of the synthetic benchmarks                                 | 44 |

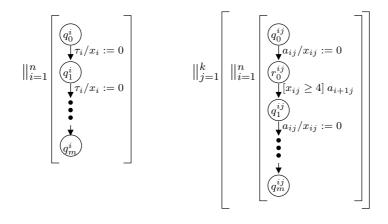

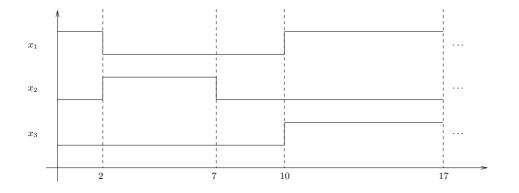

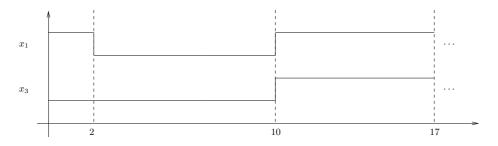

| 4.1 | A signal over the Boolean variables $\{x_1, x_2, x_3\}$                   | 52 |

| 4.2 | The signal of Figure 4.1 projected on $\{x_1, x_3\}$                      | 54 |

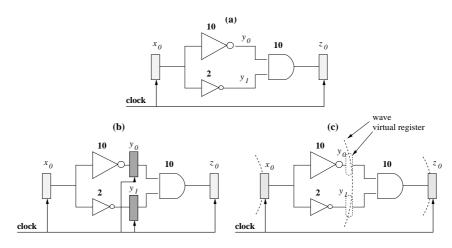

| 5.1 | Example: clocked circuit; a pipelined circuits; a wave-pipelined circuits | 63 |

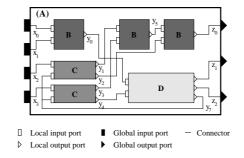

| 5.2 | Circuit structure: Graph of components.                                   | 67 |

|     |                                                                           |    |

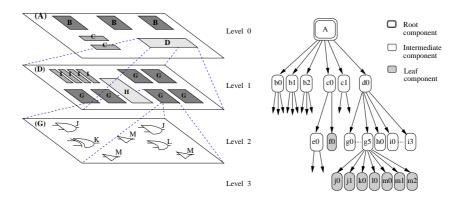

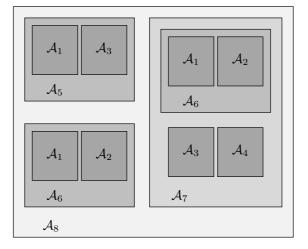

| 5.3 | Hierarchical structure of a circuit.                                                                            | 67  |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

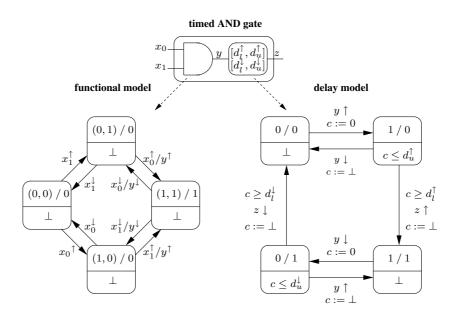

| 5.4 | A gate is decomposed into an instantaneous Boolean gate and a delay element .                                   | 70  |

| 5.5 | The timed automaton for an AND gate with propagation delay                                                      | 71  |

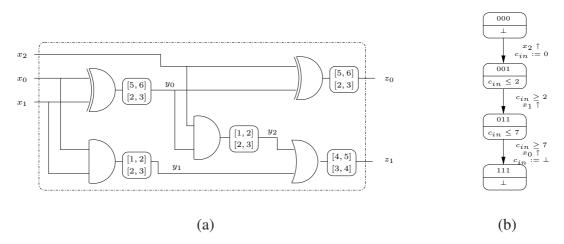

| 5.6 | A circuit example: (a) a full adder; (b) an input generator                                                     | 72  |

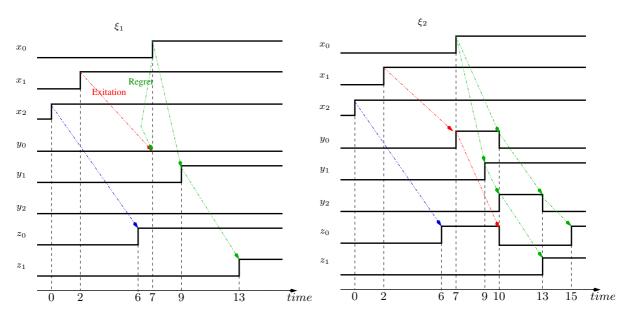

| 5.7 | The signals associated with runs                                                                                | 74  |

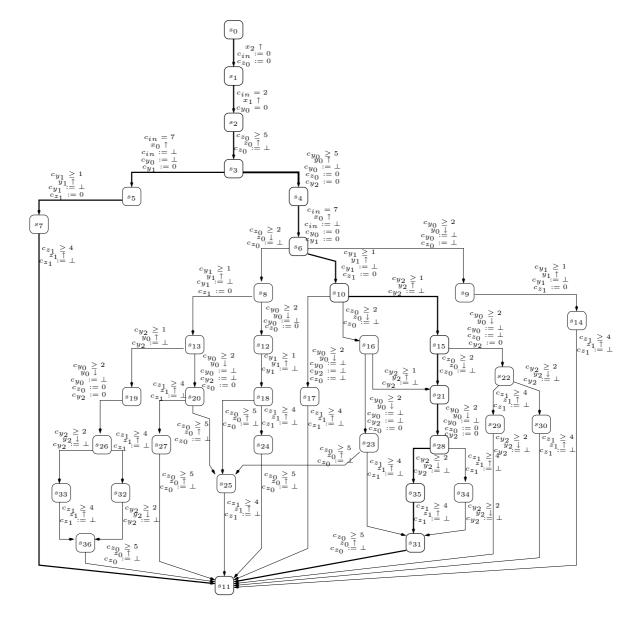

| 5.8 | The interpreted timed automaton obtained for the example of Figure 5.6                                          | 75  |

| 6.1 | The behavior added with the time projection                                                                     | 81  |

| 6.2 | Projecting on the global clock $\hat{c}$ : automaton $\mathcal{A}_X^{\hat{c}}$                                  | 83  |

| 6.3 | Projection on observable variables, automaton $\mathcal{A}_{X_{ou}}$ .                                          | 85  |

| 6.4 | Removing silent transitions, automaton $\mathcal{A}^o$                                                          | 87  |

| 6.5 | Merging bisimilar states, automaton $\mathcal{A}^b$ ; Merging transitions, automaton $\mathcal{A}^m_{X_{ou}}$ . | 89  |

| 6.6 | A compositional analysis framework for acyclic circuits with acyclic inputs                                     | 90  |

| 6.7 | A global view of the compositional approach                                                                     | 93  |

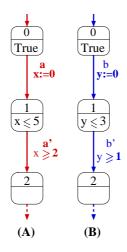

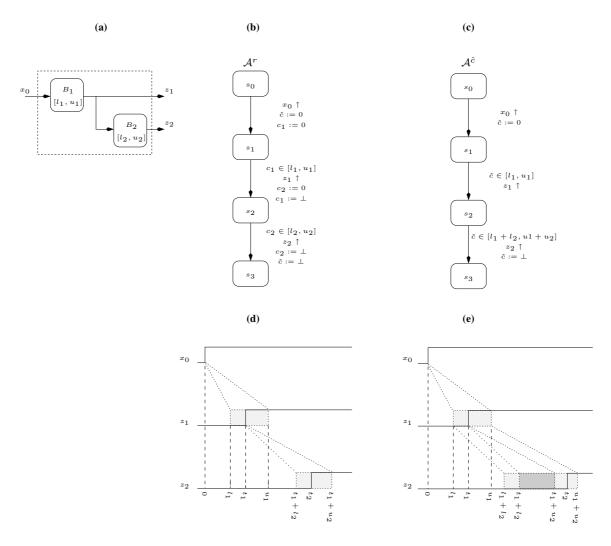

| 7.1 | Example of Component Based System                                                                               | 96  |

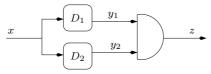

| 7.2 | An example of circuit                                                                                           | 98  |

| 7.3 | A timed automaton modeling the circuit of Figure 7.2.                                                           | 106 |

| 7.4 | The TA of Figure 7.3 with extra input clocks: $\mathcal{A}_X^{+\hat{C}}$                                        | 107 |

| 7.5 | The TA of Figure 7.4 interpreted and projected on global clocks: $\mathcal{A}_X^{\hat{C}}$                      | 108 |

| 7.6 | The result of projecting the TA of Figure 7.5 on the interface variables: $A_{X_{io}}$ .                        | 109 |

| 7.7 | The result of minimization of the TA of Figure 7.6: $\mathcal{A}_{X_{io}}^m$                                    | 110 |

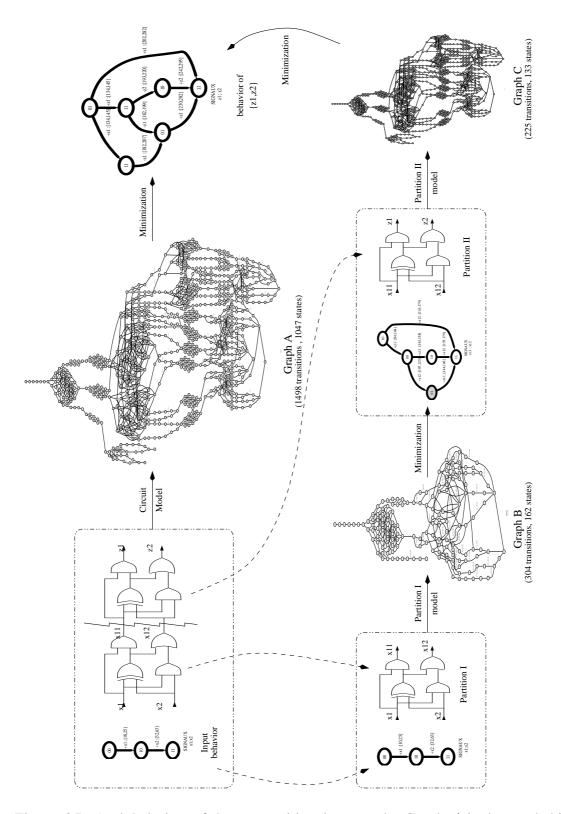

| 8.1 | A Global view of the TCA tool.                                                                                  | 115 |

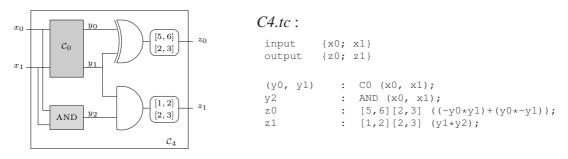

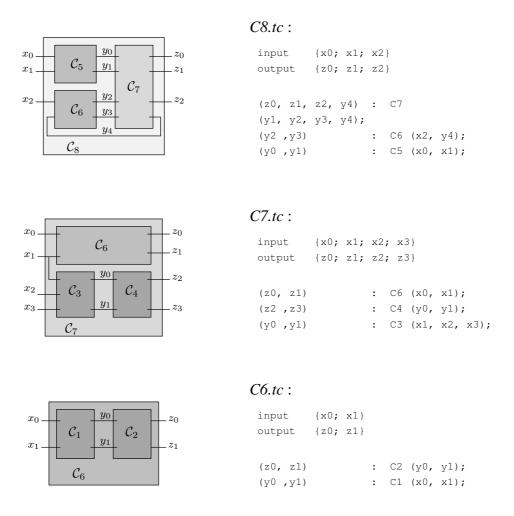

| 8.2 | A digital circuit and its structural description.                                                               | 115 |

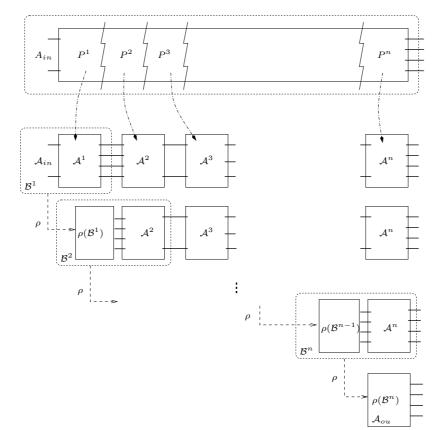

| 8.3 | The arborescent structure of a component based system                                                           | 118 |

| 8.4 | The transformation performed by the COMPILER module                                                             | 119 |

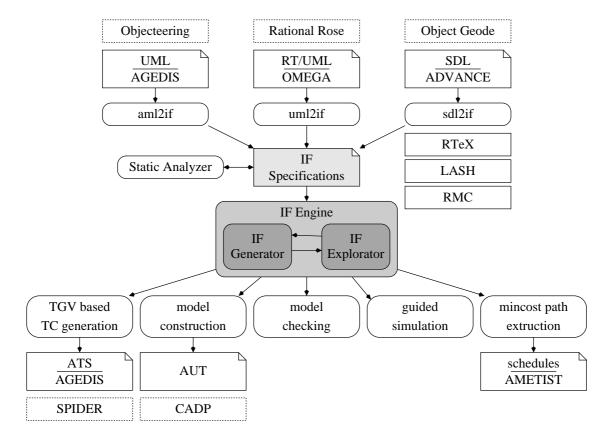

| 8.5 | The IF-toolbox.                                                                                                 | 120 |

| 8.6 | An overview of the ENGINE module.                                                                               | 121 |

# **List of Tables**

| 3.1 | Experimental results on the synthetic acyclic benchmarks.      | 44 |

|-----|----------------------------------------------------------------|----|

| 3.2 | Results on the Fisher protocolbenchmark.                       | 45 |

| 6.1 | Comparing the performance of direct and compositional analysis | 92 |

# **Chapter 1**

# Introduction

This thesis is part of an effort to make formal verification of *timed* models of hardware and software systems applicable to industrial size problems. This effort is inspired by the developments that took place in the last 30 years in the domain of *algorithmic verification* of discrete untimed models. Hence we open this chapter with a very quick introduction to formal verification and its role in the design process, followed by the major motivations for extending it to timed models and a high-level survey of the development of verification tools for timed automata.

### **1.1 Formal Verification**

Hardware and software systems are inevitably growing in scale and functionality leading to very complex systems. In such systems the likelihood of subtle errors is increasing substantially. To avoid undetected bugs which can be extremely expensive<sup>1</sup> to repair, verification and validation procedures have taken a central place in the design flow of contemporary systems.

The most prevalent approach to design verification is simulation. Within this approach one analyzes the response of a *model* of the system to a series of stimuli, that is, possible scenarios of input events. Although this process can detect bugs, it cannot guarantee correctness because the number of such scenarios is prohibitively large, if not infinite. Much of the work in this area is concerned with finding a representative sample of the input stimuli which "covers", in some sense, all the interesting cases. The correct functioning of the system in the presence of these stimuli can increase our confidence in its overall correctness but the number of such test cases can be extremely large. In many application domains verification has become the major bottleneck in design flow and may represent up to 80% of the overall design cost. With marketing pressures demanding shorter and shorter design cycles, for larger and more complex

<sup>&</sup>lt;sup>1</sup>Especially in hardware if the bugs are discovered after fabrication.

products, it has been recognized that traditional verification practices, which are mostly test based, are not sufficient and complementary methods are needed to meet the design validation challenge. Formal verification suggests an alternative approach to tackle these problems.

Formal methods refer to mathematically rigorous techniques to establish design correctness. The correctness of a system (design, implementation) is defined relative to its *specification* which reflects our expectations from the observable behavior of the system. Mathematically speaking, a formal specification should unambiguously distinguish correct and incorrect system behaviors. Formal logic is considered as the universal formalism for formalization. However, since we are interested in the *dynamic* behavior of systems, *temporal logics* which allow us to express more naturally the succession of events in time, turned out, following the suggestion of Pnueli [Pnu77, Pnu81], to be a more natural and popular specification formalism [MP91, EF06].

The other ingredient of the verification process (formal and informal verification alike) is a mathematical *model* of the system dynamics. Such a model should be, in terms of observables, at least as detailed as the specification so that the behaviors it generates can be checked against it. In addition, it should be sufficiently detailed to include the features that are essential for correctness. A model not satisfying this requirements will be at the risk of generating spurious counterexamples, namely, exhibiting incorrect behaviors which are impossible in a more detailed model of the system. On the other hand, the model should be as abstract as possible to make verification tractable. To give some examples, functional correctness of Boolean gate-level models of circuits can be done while abstracting away from electrical properties of transistors, while correctness of communication protocols is performed on models that focus on the *control* structure and ignore the contents of the *data* which is transmitted.

The mathematical models used in both software and hardware verification are essentially *discrete transition systems (automata)*. In software such models can be derived from the actual code by abstracting the values of variables and complex data structures. In hardware, such models are often based on models already used by CAD tools for simulation and synthesis. Such models exist at various levels of abstractions ranging from silicon and transistor models, via Boolean networks up to high-level functional models. Formal verification of hardware is traditionally done at the RTL (register transfer level) and gate levels which are modeled naturally as finite-state automata. Recently attempts have been made to extend formal verification toward higher levels (SystemC) as well as to lower levels that involve electricity and time delays. As we shall see later, this work is part of the latter effort.

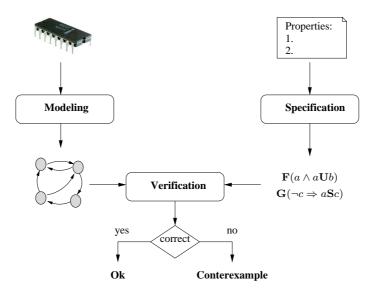

Once we have the specifications and an appropriate model of the system, we can start the verification process whose aim is to provide a proof that the system satisfies the specification, that is, all the behaviors it may exhibit are correct. Two basic proof methodologies can be used to establish this fact, one is *deductive*, that is, using *theorem proving* and one is *algorithmic*, best

#### known as model-checking.

The deductive approach consists of using a set of *axioms* and *inference rules* to prove that the system satisfies its specification. Such proofs are typically long and tedious and theorem proving tools may help a lot in the book keeping associated with the process. However, there is no way to replace the human in the loop for suggesting auxiliary theorems and proof strategies. Hence the process is only partially automated and requires highly-skilled professionals with a lot of patience and understanding of the design. A deductive framework for linear-time temporal logic is presented in [MP95b].

The algorithmic approach, the source of inspiration for this thesis, uses graph algorithms to explore all the paths in a *finite-state* model of a system. The behaviors that correspond to these paths are checked against the specifications. The idea of model checking for temporal properties was introduced in the seminal papers of Clarke and Emerson [CE81], and Queille and Sifakis [QS82] for the branching-time temporal logic CTL and was later extended to the linear-time LTL in [LP85]. In automata-theoretic terms this process can be viewed as checking containment between two  $\omega$ -regular languages, one generated by the system and the other derived from the specification [VW86]. Other approaches to verification used automata also as a specification formalism [HK90, Kur94]. There are many variants of model checking problems that differ in the choice of specification formalisms, the conformance relation used to compare implementation and specification (trace inclusion, refinement ordering, observational equivalence [CPS93]), etc. More on the topic can be found in books such as [CGP99, BBF<sup>+</sup>01].

Unlike theorem proving, model checking is, in principle, fully automatic: the user provides a high-level representation of the model and the specifications to be checked, and the model checker can decide correctness without further intervention. If it turns out that the specification is not satisfied by the model, a *counterexample* is produced. Counterexamples represent, perhaps, the most valuable outcome of model checking as they may capture subtle errors in the design that could pass unnoticed by non-exhaustive simulation.

The main limitation of model-checking is that, in general, it requires exploring the complete state graph of the model, a graph whose size increases exponentially with the number of system components. This problem, known as the *state explosion problem*, has always been considered as a major barrier which, for a long time, has restricted the applicability of this methodology to verify rudimentary sized systems.

Dealing with the state explosion is still one of the major research concerns in algorithmic verification. Several breakthroughs took place over the years, including *symbolic* model checking [BCM<sup>+</sup>90, McM92b] which, by representing sets of states via Boolean formulae, provided for the analysis of huge transition graphs which could not be explicitly enumerated. Another performance improvement, known as *bounded model checking* [BCC<sup>+</sup>03], takes advantage of the

Figure 1.1: Model Checking.

capabilities of modern SAT solvers to check whether all system behaviors up to certain length are correct. Although these techniques cannot change the inherent computational hardness of the verification problem, they succeeded in increasing the size of practically verifiable systems by several orders of magnitude and moved formal verification from theory to practice.

Beyond the contribution of these and other techniques, the only scalable way to cope with state explosion is to use the same principles used by the designers of complex systems, that is *compositional* (modular, hierarchical) reasoning. The underlying observation is that a designer of a component of a complex system does not maintain in his head the huge global transition graph associated with the whole system. An individual component is designed to work properly based on a small abstract model of its environment (the rest of the system) which focuses on those aspects of the other parts of the system which are relevant for the interaction with the component. Compositional proof methodologies such as *assume-guarantee reasoning* are subject to ongoing research, and like in theorem proving, a major issue here is the *automatic* generation of abstract models of components. Much of this thesis will be concerned with automatic abstraction of timed systems.

### **1.2 Timed Systems**

The level of abstraction of discrete transition systems is very useful for proving functional correctness but it is not sufficiently detailed for certain purposes. We will illustrate this claim using two classes of applications, one from hardware and one from software.

#### 1.2. TIMED SYSTEMS

Delays in Circuits: Suppose we realize a synchronous sequential machine using gates and latches. The discrete abstraction of the system as an automaton is valid if the time it takes for the gates to compute the next-state function is always smaller than the period of the clock. To see whether this relation between period and maximal delay holds or to compute the maximal frequency in which the circuit can work, we need to refine the gate model from an instantaneous Boolean function into a model where the output reacts to a change in its input within some propagation delay. In industrial practice, timing analysis and functional verification are often done separately: first, the maximal frequency is determined by approximating the maximal delay of the circuit by the sum of delays along the longest path from input to output, regardless of the logic. This process is called *static timing analysis* to distinguish it from simulation which considered "dynamic". After that, functional verification is pursued on the untimed model. While this separate treatment of logic and timing is the only practical way to cope with the complexity of large circuits such as processors, it is clear that the full picture on the systems behavior is obtained by combining the logic and timing into one model. For example, it might be the case that due to the logical structure of the circuit, the longest path is a "false path" and cannot be exercised by any input scenario. A more detailed model which interleaves discrete changes with propagation of delays will be more faithful to the dynamics of the circuit. Such models can also be useful for analyzing asynchronous circuit that operate without a central clock and to which static timing analysis is difficult to apply.

**Performance of Real-time Software**: The terms *real-time* or *embedded* software are often used to denote systems that interact with the external physical world, for example control of airplanes, cars and other complex systems. In such interactions, the importance of timely response cannot be underestimated, and the system may become useless, or even dangerous, if it produces the right result in the wrong time. Less safety critical, but economically no less important are systems that process and transfer streams of data of various types (communication, music, video). In such systems the so-called *quality of service* can make the difference between a useful and a useless system.

Consider a *scheduler* which receives requests for some common resources from different *clients* and allocates the resources according to some rule. Using classical verification with automata, one can prove that the scheduler does not commit errors such as allocating the same resource simultaneously to two or more clients (mutual exclusion) or entering a state where no client can progress (deadlock avoidance). There are, however other properties of interest which are not captured by the discrete model. Suppose the clients are real-time programs that need to complete their execution within some *deadline*. In order to check whether a given scheduler guarantees that every client will be serviced within its respective deadline, we need to introduce into the model *quantitative* timing information such as the expected execution time of each type

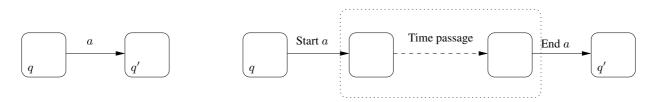

of client, the constraints on the time between successive arrivals of clients, etc. As in the case of circuits, incorporating this kind of information amounts to refining the way we model the act of executing a piece of code. In the traditional modeling with automata, such an act could be seen as a *instantaneous action*, while in a timed model it is split into a sequence consisting of: 1) the discrete event of starting the process; 2) passage of time during the execution; and 3) the discrete event of termination (see Figure 1.2). Only on the basis of this quantitative information one can check whether such a system meets its deadlines or infer other time-related performance measures such as throughput and latency.

Figure 1.2: Refining a discrete transition into a process that takes time.

It is worth observing that like in static timing analysis, early work on real-time scheduling was based on separation of concerns. In the classical Liu and Layland model [LL73], the tasks are assumed to be unrelated to each other (except for requiring the same processor) and to arrive with a fixed period. Hence their schedulability could be computed cheaply according to an analytic condition on their deadlines, periods and execution times. However, it is commonly recognized that such techniques are not satisfactory for modern and complex systems that admit sporadic arrivals, more complex inter-dependence among tasks, combination of hard and soft constraints and multi-processors.

These two application domains show the need for models that combine *discrete events* with *time passage*, models that can capture the competition between parallel processes and the subtle interaction between logic and timing. Such models augment the discrete state variables of a system with additional variables that measure the elapse of time between events. Using these variables one can express the *duration* of processes by measuring the evolution of such variables. Various approaches have been proposed for extending transition systems with quantitative timing information, for example timed variants of Petri nets [Ram74, MF76, BD91, Rok94], timed discrete-event systems [BW94, CL06] and Max-Plus systems [BCOQ93]. The most fruitful approach to these problems came from the verification community which at the end of the 80s started exploring the extension of verification methodology toward real time systems, for example, [dBHdRR92].

Most of the current literature and tools in algorithmic timed verification is based on the *timed automaton* model, an automaton augmented with real-valued clock variables, first introduced

formally in the seminal paper of Alur and Dill [AD90, AD94]. Other models proposed around the same time are the *timed transition systems* of Henzinger, Manna and Pnueli [HMP92] and a precursor of timed automata proposed by Dill [Dil89] based on counters, clocks that go down to zero. The results of [AD90] showed that the basic verification-related questions such as language and  $\omega$ -language emptiness, are decidable in this model despite its infinite state space. The complexity of these problems was shown to be PSPACE-complete, at least as hard as untimed verification. It is interesting to note that the finite-quotient property underlying this decidability result has been discovered much earlier by Berthomieu and Menasche in the context of timed Petri nets [BM83] but did not have a similar impact at that time.

Since the publication of [AD90] several research groups worked on various theoretical aspects of timed automata and on building progressively more efficient verification tools based on this model. The decidability result of [AD90] was based on transforming the timed automaton into a finite quotient, also known as the *region graph*, on which discrete verification algorithms could be applied. This construction turned out to be impractical and further efforts focused on finding more efficient ways to perform verification. We mention some of these efforts without attempting to be exhaustive or chronological.

The tool KRONOS [DOTY95, Yov97] has been developed at Verimag under the supervision of Sifakis, starting with the theses of Yovine [Yov93], Olivero [Oli94] and Daws [Daw98]. It was initially based on the results reported at [HNSY94] for model-checking timed automata against TCTL formulae using a backward reachability algorithm, manipulating sets of clock values called *zones* which are defined by conjunctions of difference constraints among pairs of clock variables. Zones can be represented by *difference-bound matrices* (DBM), as has actually been suggested in [Dil89]. Around the same time a real time extension of the SPIN model checker [Hol97] has been developed by Tripakis using a zone-based forward reachability algorithm [TC96]. The tool OPENKRONOS has been developed in the thesis of Tripakis [Tri98] using on-the-fly forward reachability. Later, these and other ideas have been integrated into the IF toolbox [BSGS04].

The tool UPPAAL [LPY97] has been developed in collaboration between Yi from Uppsala and Larsen from Aalborg, starting with [YPD94, LPY95, BLL<sup>+</sup>95] and being the topic of the thesis of Pettersson [Pet99]. Over the years, UPPAAL has been subject to continuous large investments in many aspects that make a tool usable, including a graphical user interface which is popular among end users, and many algorithmic and software engineering improvements, see for example [ABB<sup>+</sup>01, BBD<sup>+</sup>02] and the thesis of Behrmann [Beh03]. The verification engine of UPPAAL, like that of IF is based today on on-the-fly forward reachability on zones, to be described in the next section.

While we can say that the verification of timed systems has passed the proof-of-concept phase,

there is still much to be done in fighting the state explosion problem, aggravated by the presence of the additional state variables, the clocks. Despite all the improvements made over the years, one may observe that a performance breakthrough, similar to symbolic model checking in untimed verification, has not yet taken place in the timed domain, and one cannot point out an application area where timed automata has proliferated into the daily practice. This thesis is part of an effort to change this situation, using the IF toolset [BSGS04] as an implementation medium.

### **1.3 Thesis Framework**

The goal of this thesis is to develop methods that will allow us, eventually, to analyze systems modeled by timed automata with dozens and even hundreds of components, each with its own state variables and clocks. Since our major challenge is algorithmic we have chosen to focus on large *synthetic* examples rather than on industrial case studies. Most of our work uses networks of Boolean gates with delays according to the model proposed in [MP95a] due to the facility of generating large examples within this model. This is not meant to imply that circuit models at the gate level are the most appropriate application domain. As the reader will see, the approach developed in this thesis applies to a wide class of systems, including embedded software, where the future applications of these techniques are more likely to be found.

The major contributions of the thesis are the following:

- 1. A new reachability algorithm which exploits the fact that the union of all zones reached by different permutations of a set of local actions is convex. This result removes a particular contribution to the state explosion associated with timed automata, which is due to the fact that different interleavings of the same actions lead to different zones.

- Development of a divide-and-conquer methodology for large networks of timed components, consisting of analyzing subsystems in isolation and then performing automatic abstraction on their timed automaton models, to yield small complexity approximate models. Such models can replace the more detailed models in a compositional reasoning framework.

- 3. Development of the major ingredient of this methodology, an algorithm for automatic abstraction of timed components which over-approximates their timed input-output behavior. The abstraction procedure involves some novel ideas for timed automata such as the use of *dynamic clocks* which are associated with those input events to which the system has not yet fully responded.

4. Implementation of all these ideas into a tool chain, based on IF. This includes translation from high-level circuit descriptions to timed automata, extension of the timed automaton model and verification algorithms to deal with dynamic input clocks which are created and discarded according to the propagation of their corresponding event in the circuit, and procedures for abstraction and minimization.

The rest of the thesis is organized as follows: Chapter 2 is a a quick introduction to timed automata and their verification. In Chapter 3 we present the new reachability algorithm that uses the convexity result for interleaving; Chapter 4 discusses circuit timing analysis and presents the timed circuit model used in the thesis and shows how we model such circuits using timed automata. In Chapter 5 we present the first ideas underlying our abstraction technique, starting with closed systems, that is, systems whose inputs change at most once at the beginning. The more general abstraction technique for open reactive systems is presented in detail in Chapter 6 together with some preliminary experimental results. Chapter 7 gives a relatively-short description of the implementation effort associated with these developments. Conclusion and suggestions for further research close this thesis.

# Part I

# **Timed Automata and Interleaving**

# **Chapter 2**

## **Timed Automata**

This chapter gives an introduction to the basics of timed automata to be used in the rest of the dissertation. Section 2.1 introduces timed automata informally through an example. Section 2.2 defines formally the syntax and the semantics of timed automata. The infinite transition system that a timed automaton specifies must be reduced, via some equivalence relation, into a finite graph in order to be analyzed. Section 2.3.1 focuses on the commonly-used verification approach which constructs a graph called the *reachability graph* or *simulation graph* which captures all the possible qualitative behaviors that the automaton may exhibit. Such a graph can be converted back into a timed automaton with special features described in Section 2.3.2.

Timed automata are introduced in this chapter as in the original papers, that is, with a "flattened" state space admitting no product structure. This presentation style is useful for introducing zone-based reachability techniques, but the reader should keep in mind that we want to treat large *products* of timed automata in which states are encoded using explicit discrete variables. We also adhere in this chapter to the "classical" *event-based* definitions where input-output symbols are associated with *transitions*, but when we move in subsequent chapters to circuits, we will use a state-based (or signal-based) semantics and associate input-output symbols with states.

### 2.1 Timed Automata through an Example

In this section we give the basic intuitions concerning timed automata using an example of a timed system. This example will serve in the sequel to illustrate certain definitions and transformations.

**Description of the timed system** In many systems, excessive heat, for instance, is often considered to be a pathological sign and keeping the system operating in such conditions may cause

severe problems that could be impossible to fix. To prevent such a serious damage, a component is often added to the system, to stop it if the symptoms endure. Between detection and shutdown the user is given a chance to resolve the problem and avoid the system outage. An informal description of the prevention component is given by the following operating rules:

- The component is in an *idle* state as long as the system functions properly.

- Once an anomaly is detected, a warning light is turned on to give the user a first indication.

- In addition to the warning light, the anomaly detection triggers a saving process for all the current system applications. This urgent operation is achieved within a delay  $d_{save}$  (1 minute). Meanwhile the user cannot start any repair task.

- After  $d_{save}$  time from the anomaly detection the user can intervene and try to repair the source of the problem.

- Within a delay  $d_{alarm}$  (3 minutes), if the problem has not been fixed, an additional acoustic alarm is turned on.

- The user can deactivate this alarm anytime and return to the state where only the warning light is on, and then proceed to reparation.

- However if this reparation is not achieved within a delay  $d_{alarm}$  (3 minutes) from the alarm deactivation, then the acoustic alarm will be turned on again. Further deactivating of the alarm by the user is still possible.

- If the problem has not been fixed within a total delay of  $d_{anomaly}$  (8 minutes) from detection then the system will be forced to stop immediately.

- On the other hand, if successful repair is claimed by the user then the prevention system will wait for  $d_{ensure}$  (5 minutes) before returning to its idle state. However, if the problem reappears within this delay, then the anomaly is considered as serious and the system will be shut down immediately, without further attempts to repair it.

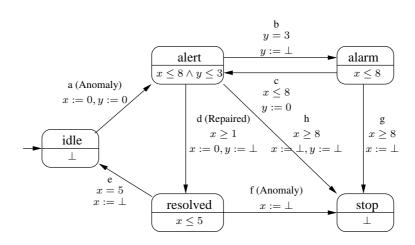

**System Modeling** Looking at these operating rules, we can notice that the system has several hard timing constraints. Timed automata are one of the natural formalisms for modeling this kind of systems. In fact, the timed automaton given in Figure 2.1 constitutes a formal model of the previously-described prevention system.

This automaton is presented as a *discrete structure* of five nodes, called *discrete states* or *locations*. Discrete states are supposed to capture all information about the current status of the

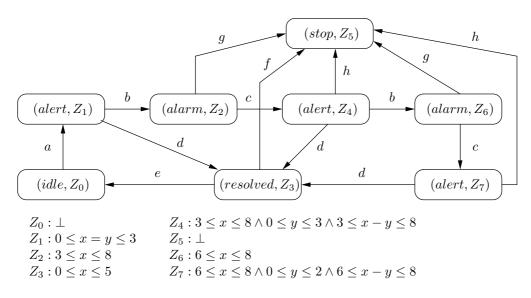

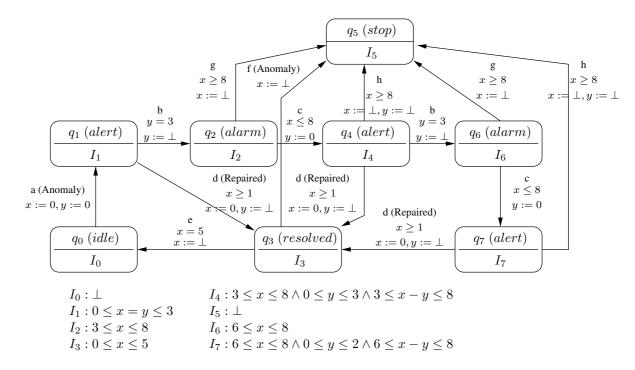

Figure 2.1: A timed automaton modeling the prevention system.

system, *except for timing information*. In the example above we have five possible states: an *idle* state which represents the normal operation mode of the controlled system; state *alert* which models the first detection of the anomaly, which means also that the warning light is turned on; state *alarm* representing the state of the system when the alarm is activated; state *resolved* which stands for the system waiting after a repair has been attempted and state *stop* modeling the situation when no successful repair has been done in time and the system is shut down by the prevention component.

The edges of this discrete structure represent *events* or *transitions* which change the discrete state of the system. For example, the anomaly detection event will make the system change its state from *idle* to *alert*. Then, a repair attempt will make it switch from state *alert* to state *resolved*. Events are considered to be *atomic* and *instantaneous*.

Notice that time progress, which is not expressed explicitly in this structure, takes place *inside* the *discrete states*. Actually, time passage is recorded using positive real variables called *clocks*. All the active clocks of the system increase synchronously at the same rate. These clocks can be set to zero, or deactivated<sup>1</sup> when a transition is taken. To model the prevention system, two clock variables x and y are used. The transition from *idle* to *alert* as well as the transition from *alarm* to *alert* are transitions that perform clock resetting.

Clocks constraints are used to restrict the behavior of the automaton by forcing it to leave a state or forbidding it from taking a certain transition. There are two different styles for expressing these constraints. In the first style that we describe below, there is a separate treatment of constraints associated with states and transitions. In the other style, advocated by [SY96, BST97], both types of information are associated with the *transitions*.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>This concept of clock deactivation will be explained in the sequel.

<sup>&</sup>lt;sup>2</sup>Note that by transition we mean here a transition of one component of a system which will correspond to a

Constraints on states are expressed using staying conditions called *invariants* [HNSY94] which are timing conditions related to each discrete state. The automaton may stay in the state (while the active clocks are progressing) as long as the state invariant holds, otherwise it has to *leave* the state via one of the enabled transitions.

The second type of timing constraints are the transition guards. A transition can be taken only if its guard constraint is satisfied. For instance, in the given example, the system can stay at the *alert* state as long as the invariant  $(x \le 8) \land (y \le 3)$  is satisfied. From this state, the transition labeled by d (anomaly repair) can be taken only after the value of clock x exceeds the threshold  $d_{save} = 1$ , which expresses the inability to repair before application saving. Notice that there is no urgency in taking this transition and the user may as well decide not to take it at all even though its guard  $x \ge d_{save}$  is satisfied. But in any case, the automaton should leave state *alert* before clock x exceeds  $d_{anomaly}$  or clock y exceeds  $d_{alarm}$ . Hence transition d could be taken at *any time* in which the value of clock x is in the time interval  $[d_{save}, d_{anomaly}] = [1, 8]$ . The ability to take a transition anywhere within an interval of time introduces a *dense nondeterminism* which is a very useful modeling feature when we have uncertain information about process durations. The upper bound of the interval is urgent and the system *must* leave the "alert" state when x = 8. If at that time no transition is enabled then the system will be in a *blocking state*. We will avoid such blocking situations in our modeling approach.

The last notion that we present via this example is that of *clock activity*, first introduced by Yovine and Daws [DY92] in order to reduce the number of clocks and the complexity of timed verification. A clock is said to be active at some discrete state when its value is relevant for the *future evolution* of the system, for example, when the clock appears in the state invariant or in a guard of a transition outgoing from the state. In the automaton of Figure 2.1 the value of clock y is not relevant at state *resolved* because the only references to its value are in state *alert* and its outgoing transition, and all the paths from *resolved* to *alert* reset this clock without testing its value. Hence we can conclude that clock y is inactive in state *resolved*.

The work of [DY92] had two major parts. The first was the (approximate) detection of such clock inactivity by performing a syntactic data-flow analysis of the automaton. Then this information was used to reduce the dimensionality of the clock space, by manipulating in each state polyhedra whose dimension is equal to the number of clocks active in this state. In our modeling framework we express clock deactivation *explicitly* by assigning a clock value to  $\perp$  and, as we shall see, in the class of automata that we use for modeling, clock activity tracking is self-evident and we can benefit from the dimensionality reduction without performing the analysis.

family of transitions in the global automaton after composition.

### **2.2 Preliminary Definitions**

The major novelty in timed automata is the connection between the discrete dynamics and the timing constraints. To express such relations we need to be able to speak of clock constraints and resets and of sets of clock valuations encountered during the verification process. We use  $\mathbb{Z}$  and  $\mathbb{R}$  to denote, respectively the integer and real numbers, while  $\mathbb{N}$  and  $\mathbb{R}_+$  will stand for their respective non-negative restrictions. Throughout this thesis we will use  $\mathbb{R}_+$  as the time domain on which clock variables range, but most of the definitions will hold also for  $\mathbb{N}$ . We use  $\mathbb{R}_{\perp}$  to denote  $\mathbb{R}_+ \cup \{\bot\}$  were  $\perp$  is a special symbol meaning "inactive" or "irrelevant". We extend the addition operation to  $\mathbb{R}_+$  by letting  $\bot + d = \bot$ .

#### 2.2.1 Clocks, Time Constraints and Zones

#### **Clocks and Valuations**

Let  $C = \{c_1, ..., c_n\}$  be a finite set of variables called *clocks*, each ranging over  $\mathbb{R}_{\perp}$ . A *clock* valuation is a function  $v : C \to \mathbb{R}_{\perp}$  assigning to each clock  $c \in C$  its value v(c). The set of possible valuations of C is then  $\mathbb{R}^n_{\perp}$ . A clock c is said to be *active* in valuation v iff  $v(c) \neq \bot$ , otherwise it is *inactive*. Due to the distinction between active and inactive clocks, we will have to deal with clock valuations of varying dimensionality. Given some  $C' \subseteq C$ , we use  $\mathcal{V}_{C'}$  to denote valuations in which  $v(c) \neq \bot$  iff  $c \in C'$ . Elements of  $\mathcal{V}_{C'}$  are then non-negative real vectors (points) of dimension  $|C'| \leq n$ . The projection operation v' = v/c' maps elements of  $\mathcal{V}_C$  to elements of  $\mathcal{V}_{C'}$  by letting v'(c) = v(c) if  $c \in C'$  and  $v'(c) = \bot$  otherwise.

In timed automata, clock valuations change due to two types of activities: *time progress* which happens inside a discrete state and *clock assignments* which take place during discrete transitions:

*Time progress:* Let d be a non-negative real. We say that clock valuation v' is the result of applying d-time-progress to clock valuation v, denoted by v' = v + d, if for every clock c, v'(c) = v(c) + d. Note that by the definition of addition on  $\mathbb{R}_{\perp}$ , all the clocks inactive in v do not change their value while all the other clocks advance uniformly.

*Clocks assignments:* A clock assignment is a function  $\gamma : \mathbb{R}^n_{\perp} \to \mathbb{R}^n_{\perp}$  indicating a transformation of clock values which occurs during a transition. The type of assignments that we allow in the definition of timed automata is restricted to compositions of one or more of the following basic assignments:

- $c_i := 0$  (resetting to zero)

- $c_i := \bot$  (deactivation of a clock)

- $c_i := c_j$  (clock copying)

We denote by  $v' = \gamma(v)$  the fact that v' is the result of applying assignment  $\gamma$  to clock valuation v and use  $\gamma_1 \circ \gamma_2$  for composition of assignments. The set of all assignments obtained by arbitrary compositions of basic assignments is denoted by  $\Gamma_C$ . We use the shorthand  $r_{C'}$  to denote resetting all the clocks in some  $C' \subseteq C$  and  $kill_{C'}$  to denote the deactivation of these clocks. We define the restriction of some  $\gamma \in \Gamma_C$  to a set of clocks  $C' \subseteq C$  as the assignment  $\gamma/_{C'} \in \Gamma_{C'}$  obtained from  $\gamma$  by removing all basic assignments that mention clocks outside C'.

#### **Clocks Constraints**

Clocks constraints are used to express the influence of clock values on the discrete dynamics (invariants and transition guards). We restrict ourselves to a family of constraints that we denote by  $\Psi_C$ , defined by the following grammar:

$$\psi ::= true \mid c_i \prec k \mid c_i - c_j \prec k \mid \psi \land \psi$$

where  $c_i, c_j \in C$ ,  $k \in \mathbb{N}$  and  $\prec \in \{<, \leq, =, \geq, >\}$ . The constraints of the form  $x \prec k$  and  $x - y \prec k$  are called *atomic*.

We define the *restriction* of some  $\psi \in \Psi_C$  to a set of clocks  $C' \subseteq C$ , denoted by  $\psi/_{C'}$ , as the constraints syntactically obtained by adding to the  $\psi$  all the minimal constraints of the form  $c \leq d$  and  $c - c' \leq d$  which are implied by the constraints in  $\psi$ , and then removing all the constraints that mention a clock outside of C'.

#### **Timed Zones**

Clock constraints define subsets of the set of clock valuations, those that satisfy them. These are subsets of  $\mathbb{R}^m_+$  where  $m \leq n$  is the number of active clocks in the state where they are evaluated. We will always assume that constraints evaluated in a state mention only variables that are active in that state. We use  $v \models \psi$  to denote the fact that valuation v satisfies a clock constraint  $\psi$ , and  $\llbracket \psi \rrbracket$  to denote all satisfying valuations.

Every constraint  $\psi \in \Psi_C$  is a conjunction of *atomic constraints*. Knowing that the set of valuations satisfying an atomic constraint defines a *half-space*, every constraint  $\psi \in \Psi_C$  will define a *convex polyhedron* which is the intersection of those half-spaces. We use, in addition to  $[\![\psi]\!]$ , the notation  $Z_{\psi}$  for this polyhedron and call it the *timed zone* associated with  $\psi$ . The set of all the zones defined on C will be denoted  $Z_C$ . Since the half-spaces are either orthogonal  $(c_i \prec k)$ or diagonal  $(c_i - c_j \prec k)$  with integer k, the vertices of these polyhedra are integer points and there is a finite number of zones in any bounded subset of  $\mathbb{R}^n$ .

**Remark**: It is a well-known fact in the theory of timed automata that there is a constant l, the largest constant appearing in the clock constraints of an automaton, beyond which further changes in the value of clock c do not matter for any constraint of the form  $c \prec k$  because substituting any l' > l instead of l for c will preserve the truth value of the constraint. Hence, for all practical purposes, we can see clock valuations as ranging over [0, l], implying a finite number of zones. However, as shown in [Bou02], this fact should be exploited with care, otherwise, subtle bugs related to difference constraints can be manifested. We do not get into the details of this technical issue in this thesis to avoid making the definitions and notations heavier. The automata that we use in this thesis do not use difference constraints in their definition.

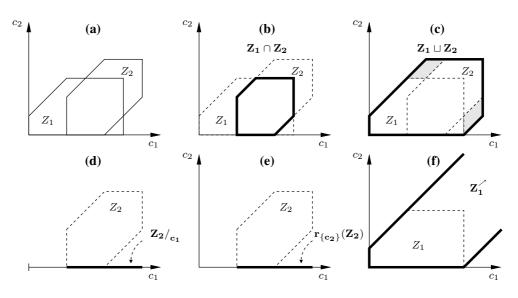

In the following we will define some useful operations on zones that will be used throughout this document. Let  $C' \subseteq C$  be a set of clocks, and let  $Z_1, Z_2 \in \mathcal{Z}_C$  be two timed zones defined on C, then:

Figure 2.2: Operations on timed zones.

$Z_1 \cap Z_1$  is the *intersection* of two zones  $Z_1$  and  $Z_2$ , which is a convex zone, see Figure 2.2-(b).

$Z_1 \sqcup Z_2$  is what we call the *timed convex hull* of the two zones  $Z_1$  and  $Z_2$  defined as:

$$Z_1 \sqcup Z_2 = \min\{Z \in \mathcal{Z}_C \mid (Z_1 \subseteq Z) \land (Z_2 \subseteq Z)\},\$$

that is the smallest (in terms of inclusion) timed zone containing both  $Z_1$  and  $Z_2$ , see Figure 2.2-(c). Since zones are not closed under union,  $Z_1 \sqcup Z_2$  can be used as an over-approximation of  $Z_1 \cup Z_2$ .

Z' is what we call the *forward projection* of Z, that is, all clock valuations that can result by applying time progress to elements of Z:

$$Z^{\checkmark} = \left\{ v \in \mathcal{V}_C \, | \, \exists d \ge 0, \, v - d \in Z \right\},$$

see Figure 2.2-(f).

$Z/_{C'}$  is the projection of a zone Z on a clock subset  $C' \subseteq C$ :

$$Z/_{C'} = \{ v/_{C'} \mid v \in Z \},\$$

see Figure 2.2-(d). This operation is related to clocks deactivation.

$\gamma(Z)$  is the result of applying the clock assignment function  $\gamma$  to all the elements of Z:

$$\gamma(Z) = \{\gamma(v) \mid v \in Z\}.$$

As we did previously we will distinguish two particular instances of this operation:

$r_{C'}(Z)$  is the *resetting* of the clocks within the set  $C' \subseteq C$ , see Figure 2.2-(e).

$kill_{C'}(Z)$  is the *deactivation* (or "killing") of clocks of the set C'. Note that  $kill_{C'}(Z) = Z/_{C \setminus C'}$ .

It is important to note the difference between  $r_{C'}(Z)$  and  $kill_{C'}(Z)$ . Applying  $kill_{C'}$  we may reduce the dimensionality of the *space* on which the zone is defined. Applying  $r_{C'}$  we may reduce the dimensionality of the *set* but *not* of the space on which it is defined<sup>3</sup>, and after some time progress the set will regain its reduced dimensions. It is not hard to see that zones are closed under all the above operations. Moreover, all these operations can be computed efficiently on a DBM representation of the zones. More details can be found, for example, in [Yov93].

#### 2.2.2 Timed Automata Syntax and Semantics

**DEFINITION 2.1 (Timed Automaton)** A timed automaton is a tuple  $\mathcal{A} = (Q, q_0, C, \Sigma, I, \Delta)$ where:

<sup>&</sup>lt;sup>3</sup>In fact, we may increase the dimension if we reset a clock which was previously inactive.

$q_0 \in Q$  is the initial state

- *C* is a finite set of clocks,

- $\Sigma$  is a finite set of labels,

- $I \in Q \to \Psi_C$  is a function associating a staying condition (invariant) with every state q. The automaton is permitted to stay at q only as long as the clock constraint I(q) is satisfied.

$$\Delta \subseteq Q \times \Psi_C \times \Sigma \times \Gamma_C \times Q$$

is the transition relation consisting of elements of the form  $e = (q, g, a, \gamma, q')$ where:

$$q, q' \in Q$$

are, respectively, the source and the target of the transition,

- $g \in \Psi_C$  is an enabling condition called the transition guard. It restricts the execution of the transition to clock valuations that satisfy it.

- $a \in \Sigma$  is the transition label,

- $\gamma \in \Gamma_C$  is a clock assignment function which takes place during a transition.

We assume, without loss of generality, that from every state q there is at most one transition labeled by a for every  $a \in \Sigma$ .

**Example** The automaton of Figure 2.1 is defined as:

$Q: {idle, alert, alarm, resolved, stop},$

$$q_0: \qquad {idle},$$

$$C: \qquad \{x,y\},$$

$$\Sigma: \qquad \{a, b, c, d, e, f, g, h\},\$$

$$\begin{split} I: & \{idle \mapsto true, \\ alert \mapsto x \leq 8 \land y \leq 3, \\ alarm \mapsto x \leq 8, \\ resolved \mapsto x \leq 5, \\ stop \mapsto true \} \end{split}$$

$\{ (idle, true, a, r_{\{x,y\}}, alert), \\ (alert, y = 3, b, kill_{\{y\}}, alarm), \\ (alarm, x \le 8, c, r_{\{y\}}, alert), \\ (alert, x \ge 1, d, r_{\{x\}} \circ kill_{\{y\}}, resolved), \\ (alert, x \ge 8, h, kill_{\{x,y\}}, stop), \\ (resolved, x = 5, e, kill_{\{x\}}, idle), \\ (resolved, true, f, kill_{\{x\}}, stop), \\ (alarm, x \ge 8, g, kill_{\{x\}}, stop) \}.$

Let us remark that it is sometimes more convenient to refer to guards, invariants and sets of clock valuations as syntactic objects (constraints) and sometimes as semantic geometric objects (zones). In order not to introduce too many notations we will use the same symbols I and g for both, so that we can write  $v \models I$  as well as  $v \in I$  or  $g \land \psi$  as well as  $g \cap Z$ .

#### **Parallel Composition of Timed Automata**

A timed automaton is often considered to be an element in a network of components running in parallel and communicating with each other. The global behavior of such a network is captured by the global timed automaton, called the *product*. There are many variations of composition depending mainly on the interaction mechanisms through which the automata influence each other. At this point we use a definition based on a *distributed alphabet* [DR95] where each component  $\mathcal{A}^i$  has its alphabet  $\Sigma^i$ . The alphabets of the components may have non-empty intersections and any global transition labeled by *a* must involve a local *a*-transition in *every* automaton  $\mathcal{A}^i$  such that  $a \in \Sigma^i$ . Independent local transitions (transitions with different labels) enabled at the same global state can be executed in *any* order (interleaving).

#### **DEFINITION 2.2 (Parallel Composition of Timed Automata)**

Let  $\mathcal{N} = \{\mathcal{A}^i = (Q^i, q_0^i, C^i, \Sigma^i, I^i, \Delta^i) \mid i \in \{1, ..., n\}\}$  be a network of timed automata. We assume the sets of clocks of each pair of automata to be disjoint and denote by  $\mathcal{J}(a)$  the indices *i* such that  $a \in \Sigma^i$ . The composition of these automata, denoted by  $\mathcal{A}^1 \parallel ... \parallel \mathcal{A}^n$  is a timed automaton  $\mathcal{A} = (Q, q_0, C, \Sigma, I, \Delta)$  where:

$Q = Q_1 \times \ldots \times Q_n$  is the set of global discrete states of the form  $q = (q^1, \ldots, q^n)$ ,

$q_0 = (q_0^1, \dots, q_0^n)$  is the initial state,

$C = \bigcup_{i=1}^{n} C_i$  is the global set of clocks,

$\Sigma = \bigcup_{i=1}^{n} \Sigma^{i}$  is the global alphabet,

$\Delta$  :

#### 2.2. PRELIMINARY DEFINITIONS

$I is the global state invariant I(q) = \bigwedge_{i \in \{1..n\}} I^i(q^i),$   $\Delta is the global transition relation consisting of tuples of the form <math>((q^1, \dots, q^n), g, a, \gamma, (q'^1, \dots, q'^n))$  such that  $\bullet \text{ for every } i \notin \mathcal{J}(a), q'^i = q^i,$   $\bullet \text{ for every } i \in \mathcal{J}(a), (q^i, g^i, a, \gamma^i, q'^i) \in \Delta^i,$   $\bullet g = \bigcap_{i \in \mathcal{J}(a)} g^i,$   $\bullet \gamma = \circ_{i \in \mathcal{J}(a)} \gamma^i$

Notice that since each assignment  $\gamma^i$  operates on a distinct set of clocks, the composition of assignments is commutative. An example of a timed automata product is given in Figure 2.3.

Figure 2.3: A timed automata product:  $C = A \parallel B$ .

#### **Semantics of Timed Automata**

Timed automata define infinite transition systems whose states are *configurations* of the form (q, v) consisting of a discrete state q and a clock valuation v. The initial configuration is  $s_0 = (q_0, \bot)$  with all clocks inactive and the transitions are either discrete transitions of the automaton or time-passage transitions. This is formalized by the notion of a step.

**DEFINITION 2.3 (Steps)** A step of a timed automaton A is one of the following:

- A discrete step: (q, v) → (q', v'), for some transition (q, g, a, γ, q') ∈ Δ such that v ⊨ g and v' = γ(v),

- A time step:  $(q, v) \xrightarrow{d} (q, v+d)$  for some  $d \in \mathbb{R}_+$  such that v + d satisfies I(q).

Note that the concatenation of two time steps is a time step:

$$(q,v) \xrightarrow{d_1} (q,v+d_1) \xrightarrow{d_2} (q,v+d_1+d_2) \equiv (q,v) \xrightarrow{d_1+d_2} (q,v+d_1+d_2).$$

Conversely, due to the dense nature of the real numbers, a time step can be split into any number of smaller time steps.

A compound step is a discrete step followed by a time step (possibly of zero duration):

$$(q,v) \xrightarrow{a,d} (q',v'+d) \equiv (q,v) \xrightarrow{a} (q',v') \xrightarrow{d} (q',v'+d)$$

A *run* of the automaton  $\mathcal{A}$  starting from a configuration (q, v) is a finite sequence of compound steps.<sup>4</sup> In the following we use the notation  $(q, v) \xrightarrow{\xi} (q', v')$  for runs.

These definitions apply to products as well. Note that a global time step in a global state  $q = (q^1, \ldots, q^n)$  is just a local (and uniform) time step for each component  $\mathcal{A}^i$ . The global invariant requires that all local invariants hold at v + d. On the other hand a global discrete step labeled by a is a local discrete step for all components  $\mathcal{A}^i$  such that  $a \in \Sigma^i$ .

**Example** The following is a run of the automaton presented in Figure 2.1. It starts at idle, where it can stay indefinitely. After 16 minutes it moves to state *alert* while detecting an anomaly and reset clocks x and y, stays at *alert* for 3 minutes without any intervention from the user, then moves to *alarm* and so on until it reaches *stop* and stays there for 14 minutes until the end of the run.

$$(idle, (\bot, \bot)) \xrightarrow{16} (idle, (\bot, \bot)) \xrightarrow{a} (alert, (0, 0)) \xrightarrow{3} (alert, (3, 3))$$

$$\xrightarrow{b} (alarm, (3, \bot)) \xrightarrow{5} (alarm, (8, \bot)) \xrightarrow{g} (stop, (\bot, \bot)) \xrightarrow{14} (stop, (\bot, \bot))$$

#### 2.3 Symbolic Reachability

Having defined timed automata and their semantics, we would like to verify them, that is, to see what the possible runs of a given automaton are, and whether they satisfy a given property. However, since the state space is infinite, simple enumeration of the possible runs is impossible. Fortunately, these runs can be grouped into equivalence classes, each consisting of runs having the same *qualitative* form in the sense that their sequences of discrete steps are identical. The

<sup>&</sup>lt;sup>4</sup>The first step can be a pure time step.

enumeration of possible runs is done in a *set-based* fashion, computing in one step all the successors of a set of configurations by an arbitrary passage of time and by transitions, as will be explained in the sequel.

The original decidability proof for verification of timed automata [AD90] was based on partitioning the state space into a finite number of equivalence classes called *regions*. Regions are the "atomic" zones from which all other zones can be constructed. Two configurations (q, v)and (q, v') are region-equivalent if for every transition guard g,  $v \models g$  iff  $v' \models g$ , and if by letting time pass they reach the same region. Hence for every sequence of regions visited by a run from (q, v) there is a run from (q, v') visiting the same sequence. The timed automaton can thus be reduced to a finite automaton whose states are regions with discrete transitions and special transitions that correspond to the passage of time. Region equivalence is guaranteed to capture all the qualitative behaviors of *any* automaton, but its force is also its weakness because the large number of regions renders this approach impractical.

Consequently, existing verification tools [DOTY95, BLL+95, BSGS04] use more efficient verification methods based on coarser equivalence relations that depend on the structure of the *particular* automaton to be verified. The most popular approach today is on-the-fly forward search based on zones. This approach has the following advantages: 1) It does not explore the parts of the state space which are not reachable from the initial state; 2) It does not refine zones beyond what is necessary and will typically result in a number of generated zones much smaller than the number of regions; 3) It uses an efficient data structure, the DBM, to store and manipulate zones.

#### **2.3.1** From Timed Automata to Reachability Graphs

The principle of symbolic reachability computation for discrete systems is to take a representation of a *set* P of states reachable after k steps, and compute from it the set succ(P) of its successors by all transitions, that is, the set

$$succ(P) = \bigcup_{q \in P} \bigcup_{a \in \Sigma} \{succ^{a}(q)\}.$$

The application of this idea to timed automata is more subtle. Successors by different transitions are treated *separately* and *enumeratively*, while the symbolic treatment is reserved for time passage and clock valuations. In other words, the basic element in the computation is an object consisting of *one* discrete state and a *set* of clock valuations. To this object one applies time passage of arbitrary duration and transitions as formalized below.

A symbolic state of a timed automaton  $\mathcal{A} = (Q, q_0, C, \Sigma, I, \Delta)$  is a pair (q, Z) where  $q \in Q$  is a

discrete state and Z is a zone. Symbolic states are closed under the following operations:

• The *time successor* of a symbolic state (q, Z) is the symbolic state (q, Z') where Z' is the set of clock valuations reachable from Z by letting time progress without violating the staying condition I(q):

$$post^{t}(q, Z) = \{(q, v + d) \mid (v \in Z) \land (d \ge 0) \land ((v + d) \models I(q))\} = (q, (Z^{\checkmark} \cap I(q)))$$

We say that (q, Z) is time-closed if  $(q, Z) = post^t(q, Z)$ .

Let (q, g, a, γ, q') ∈ Δ be a transition. The *a-transition successor* of a symbolic state (q, Z) is the set of configurations reached by taking this transition. Only clock valuations of Z that satisfy the guard g are concerned with this transition. This clock valuations will be transformed according to the assignment function γ while taking this transition:

$$post^{a}(q,Z) = \{(q',v') \mid \exists v \in Z, v \models g \land v' = \gamma(v)\} = (q',(\gamma(Z \cap g)))$$

• The *a*-successor of a symbolic state (q, Z) is the set of configurations reached from (q, Z) by an *a*-transition followed by passage of time:

$$succ^{a}(q, Z) = post^{t}(post^{a}(q, Z)) = (q', (\gamma(Z \cap g))^{\checkmark} \cap I(q'))$$

To have a better feel of the way these operations are used in a set-based computation of all the runs of a timed automaton, let us look closely at the relation between a symbolic state and its successor.

**Proposition 2.1** Let  $(q', Z') = succ^a(q, Z)$  for a transition  $(q, g, a, \gamma, q')$ . A configuration (q', v') belongs to (q', Z') if and only if it is the endpoint of a compound step

$$(q,v) \xrightarrow{a,d} (q',v')$$

for some  $(q, v) \in (q, Z)$  and some  $d \ge 0.5$

Hence computing (q', Z') amounts to computing "in parallel" the first segment of an uncountable number of runs, all starting from (q, Z) by making an *a*-transition followed by arbitrary passage of time.

<sup>&</sup>lt;sup>5</sup>Note, however, that not all elements of (q, Z) are the start points of such compound steps because for some points, the time successors will not intersect g.

Equipped with these operators under which the set of symbolic states is *closed*, we can now introduce the *forward reachability* algorithm for timed automata which computes this way all the runs of  $\mathcal{A}$ . We present the breadth-first version of the algorithm but other exploration orders are possible. The algorithm terminates because there are finitely many zones in any bounded subset of  $\mathbb{R}^n_+$ .

Algorithm 2.1 Forward reachability algorithm (breadth first).

```

Explored := \emptyset

New := \emptyset

Waiting := \{(q_0, \bot)\}

while (Waiting \neq \emptyset) do

for each (q, Z) \in Waiting do

for each (q, g, a, \gamma, q') \in \Delta do

New := New \cup succ^a(q, Z)

Explored := Explored \cup (q, Z)

Waiting := New \setminus Explored

New := \emptyset

return (Explored)

```

As a byproduct, this algorithm produces the *reachability* (or *simulation*) *graph* which can be viewed as the finite state automaton defined below.

**DEFINITION 2.4 (Reachability Graph)** The reachability graph associated with a timed automaton  $\mathcal{A} = (Q, q_0, C, \Sigma, I, \Delta)$  is a finite automaton  $\mathcal{G} = (S, s_0, \Sigma, \delta)$  such that S is the smallest set of symbolic states containing the initial state  $s_0 = (q_0, \bot)$  and closed under  $\{succ^a\}_{a \in \Sigma}$ . The transition relation  $\delta$  consists of all triples of the form ((q, Z), a, (q', Z')) such that  $(q', Z') = succ^a(q, Z)$ .

The fundamental property of the reachability graph is the following: for every sequence over  $\Sigma$  that this automaton may generate, there is a run of the timed automaton  $\mathcal{A}$  generating the same sequence of events. In other words, the timed automaton  $\mathcal{A}$  and the automaton  $\mathcal{G}$  based on its reachability graph generate the same subsets of  $\Sigma^*$  or  $\Sigma^{\omega}$ . Hence, if the properties we are interested in are purely qualitative, that is, concerned with the *order* of events, not with the *distance* between them, and if they have no alternating path quantifiers,<sup>6</sup> applying classical model checking algorithms to  $\mathcal{G}$ , we will obtain results which are valid for  $\mathcal{A}$  as well. For branching-time properties, there is a finer equivalence relation, the time-abstract bisimulation [TY01], whose induced finite-state quotient can be used for verification (and synthesis).

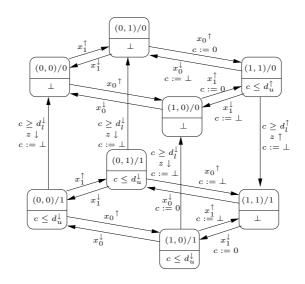

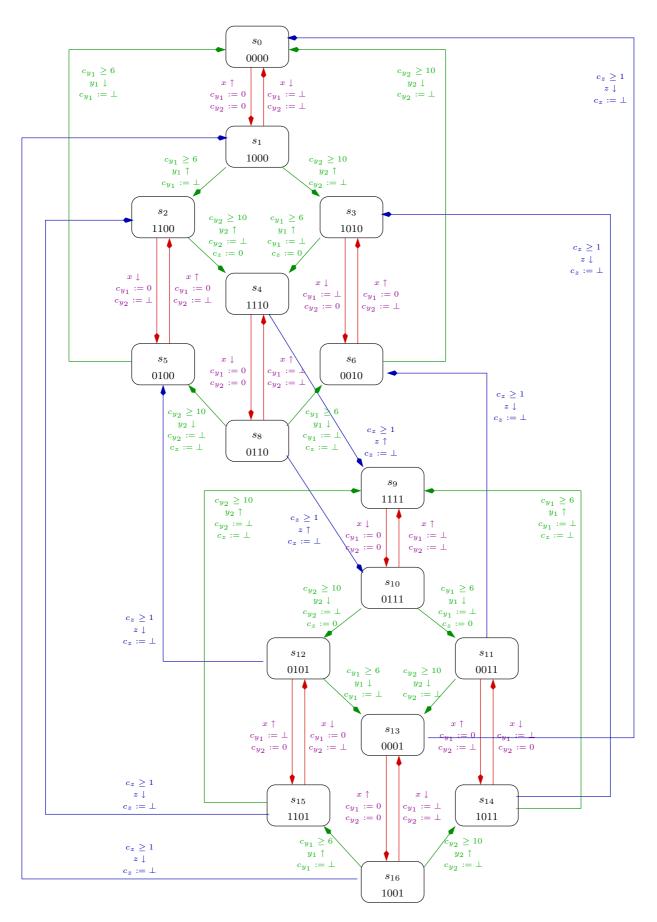

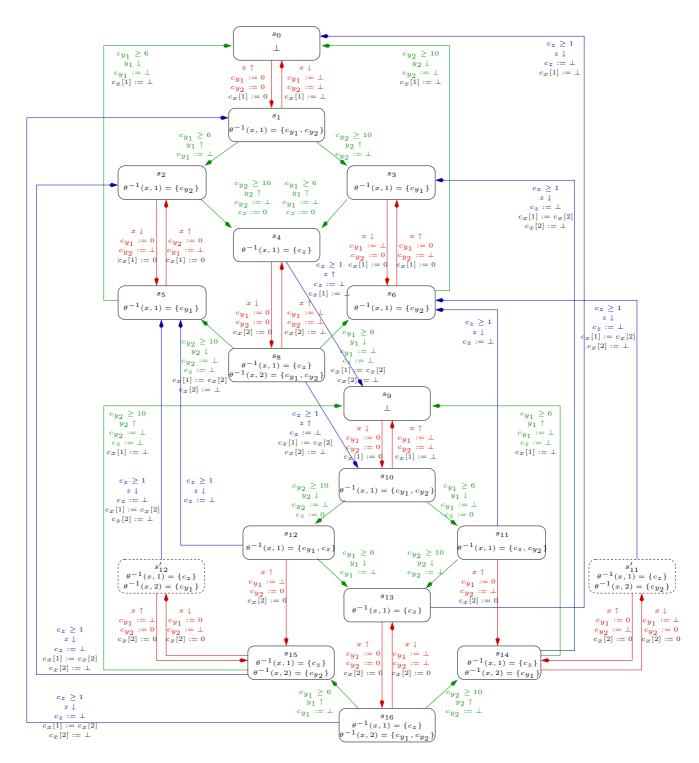

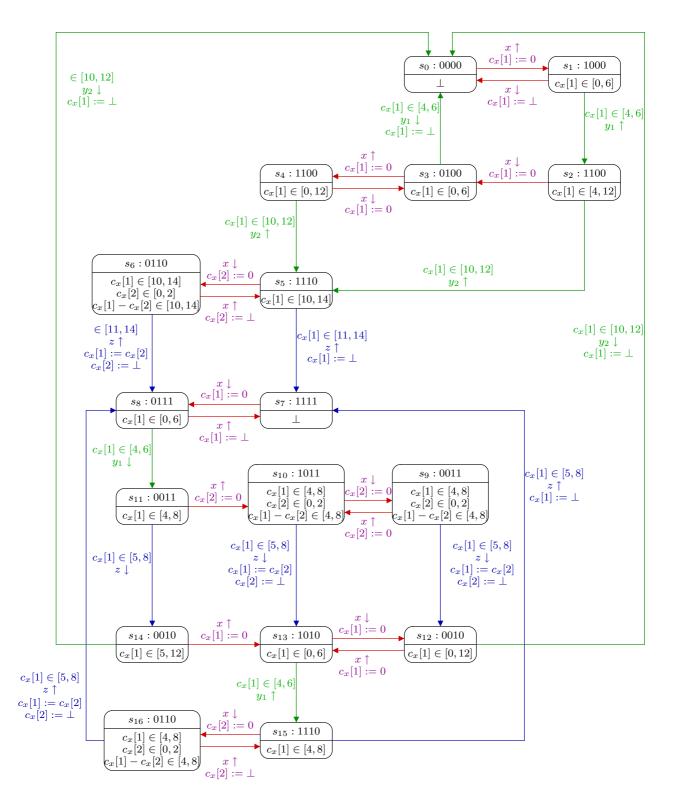

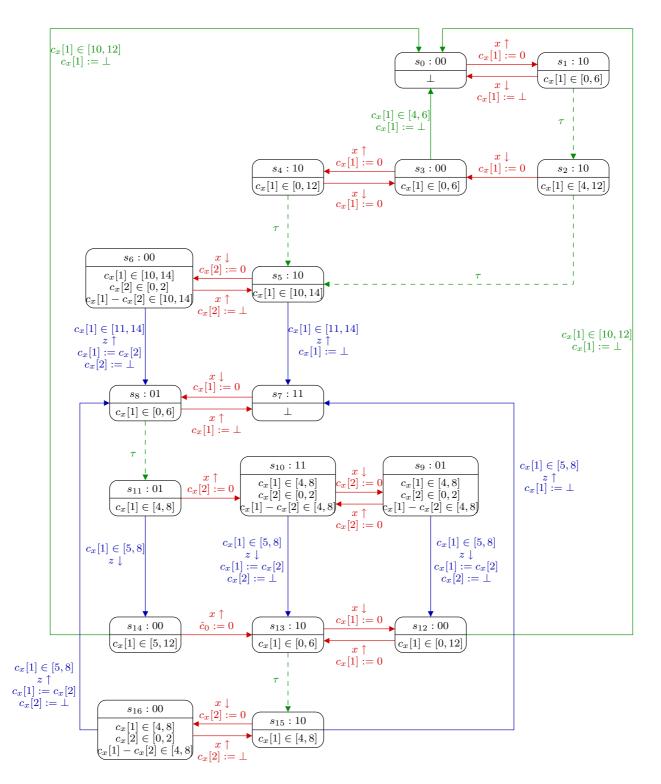

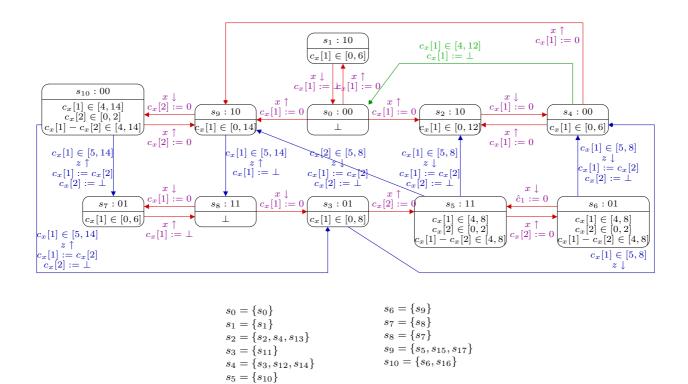

**Example of Reachability Graph** The reachability graph of the timed automaton presented as an example in Figure 2.1 is depicted in Figure 2.4. Looking at the example we see some

<sup>&</sup>lt;sup>6</sup>For example, properties expressed in LTL or in the existential or universal fragments of CTL.

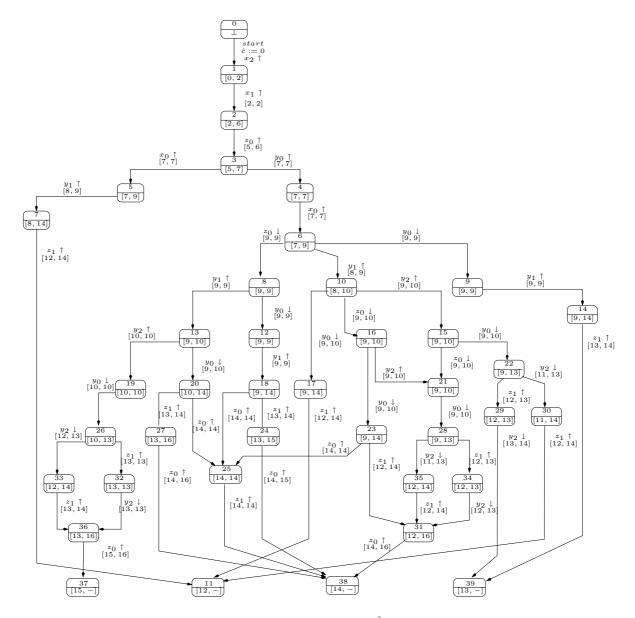

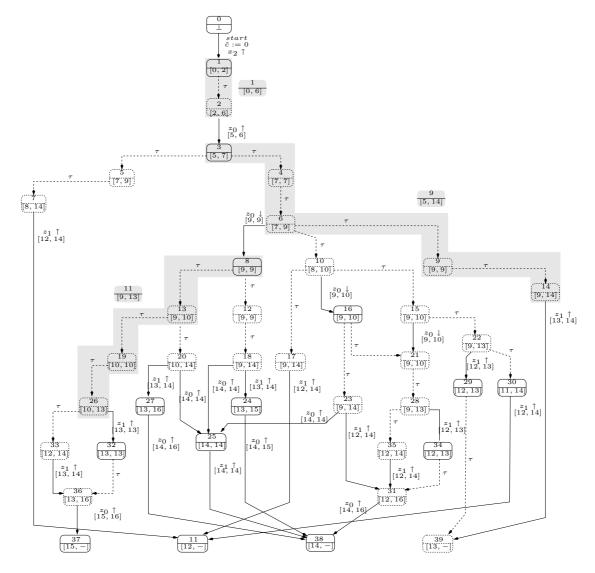

important features of the reachability graph. The first is that some discrete states of the timed automaton are "split" into several copies, each with a different zone. For example the *alert* state has three copies depending on the number of times (zero, one, or two) the alarm was set and then disabled by the user. The reason these states are considered as different is due to the different values of x which determine the number of times the alarm can be triggered before the condition  $x \ge 8$  will impose shutdown. Another important aspect of the reachability graph is that it eliminates states and transitions which are impossible according to timing constraints, for example, the transition labeled b is not possible in  $(alert, Z_7)$ . The effect of this reduction is not very visible in this example where all states are reachable, but will be more significant when we treat large *products* of timed automata where many global states may turn out to be unreachable due to competition among parallel processes.

Figure 2.4: The reachability graph of the timed automaton of Figure 2.1.

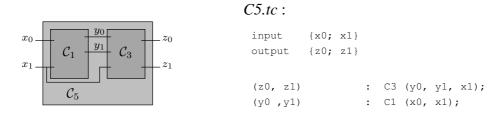

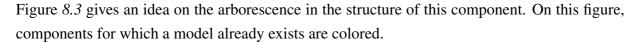

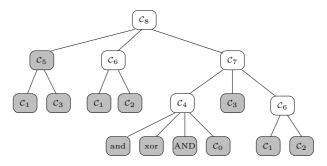

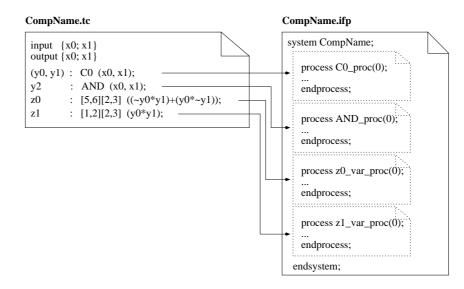

#### 2.3.2 From Reachability Graphs to Interpreted Timed Automata