# Formal and Informal Methods for Multi-Core Design Space Exploration

Jean-Francois Kempf Olivier Lebeltel Oded Maler

QAPL, April 13, 2014

# Introduction

Context A motivating example

### DESPEX

Overview DeSpEx: The Tool Case Study

Conclusion

## Context

# Minalogic project ATHOLE

- Low-power multi-processors platform for embedded systems.

- Partners: STMicroelectronics, CEA Leti, Thales, CWS, Verimag.

- Verimag: High level modeling and analysis.

# Contribution

Development of a framework for modeling and analysis of embedded systems.

## **Motivation**

# Embedded Systems Design

Several design choices both in hardware and software

## **Motivation**

# Embedded Systems Design

- Several design choices both in hardware and software

- Each has advantages according to different criteria:

- Timing performance

- Power consumption

- Platform cost

- ▶ ...

## Motivation

# Embedded Systems Design

- Several design choices both in hardware and software

- Each has advantages according to different criteria:

- Timing performance

- Power consumption

- Platform cost

- ▶ ...

# Needs

## Performance estimation as soon as possible

- evaluate quickly different trade-offs

- Exploration and Analysis on a high level of abstraction.

# **High-Level Performance Evaluation**

# Advantage

- Works at virtual level:

- No need for a physical platform

- No need for a complete implementation

- Models are simplified:

- Performance analysis is tractable

- Simulation and analysis are fast

- Evaluation of different alternatives can be done easily

# **High-Level Performance Evaluation**

# Advantage

- Works at virtual level:

- No need for a physical platform

- No need for a complete implementation

- Models are simplified:

- Performance analysis is tractable

- Simulation and analysis are fast

- Evaluation of different alternatives can be done easily

To compensate the lack of precision at this level of description:

- Increase the uncertainty margins

- Consider this uncertainty in the analysis

# Uncertainty

# Modeling uncertainty with timed automata

- Timing informations are modeled as intervals

- Exhaustive reachability analysis

- Analysis is worst-case oriented and sometimes intractable.

## Uncertainty

# Modeling uncertainty with timed automata

- Timing informations are modeled as intervals

- Exhaustive reachability analysis

- Analysis is worst-case oriented and sometimes intractable.

We may be more concerned about the average performance.

# Uncertainty

# Modeling uncertainty with timed automata

- Timing informations are modeled as intervals

- Exhaustive reachability analysis

- Analysis is worst-case oriented and sometimes intractable.

We may be more concerned about the average performance.

Modeling uncertainty probabilistically

- Duration Probabilistic Automata:

- Timed automata with probabilistic durations

- Discrete event simulation and statistical analysis

- Exact computation of expected termination time

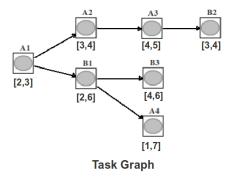

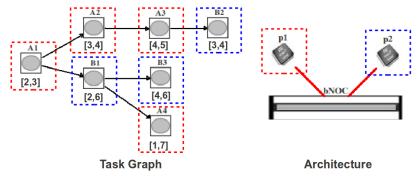

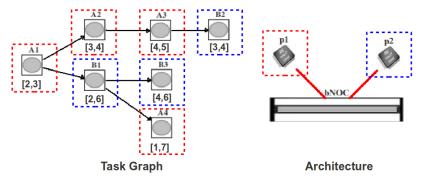

## A motivating example

We show, with this example, the importance of considering the *uncertainty* in the analysis.

## Outcome

Timing analysis based exclusively on worst case execution times might not catch the worst behavior

Context A motivating example

### **Abstract Model**

#### Architecture

Context A motivating example

#### **Abstract Model**

FIFO scheduling (non preemptive)

Context A motivating example

### **Abstract Model**

- FIFO scheduling (non preemptive)

- Question:

- What is the maximal response time of the job ?

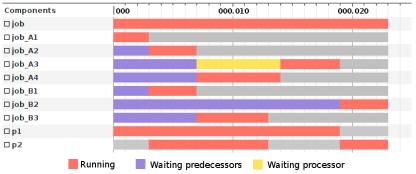

### **Corner-Case Analysis**

Naively, to get the maximal response time, one might do an analysis based on *worst-case execution time* for all tasks.

### **Corner-Case Analysis**

Naively, to get the maximal response time, one might do an analysis based on *worst-case execution time* for all tasks.

Analysis gives a response time of 19 timeunits

### **Reachability Analysis with Uncertainty**

We use now timed automata reachability analysis:

- Explore all possible behaviors.

- Retrieve the execution trace leading to the worst response time.

## **Reachability Analysis with Uncertainty**

We use now timed automata reachability analysis:

- Explore all possible behaviors.

- Retrieve the execution trace leading to the worst response time.

Analysis gives a response time of 23 timeunits

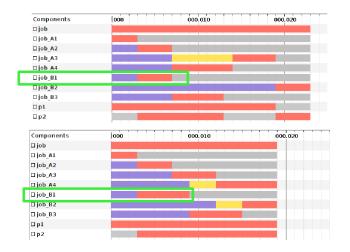

Context A motivating example

### **Explanations**

B1 takes less time  $\Rightarrow$  A4 start before A3 (on critical path).

#### A motivating example

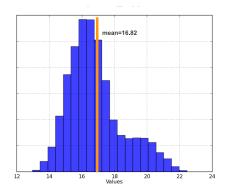

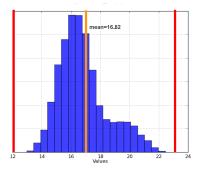

### **Quantitative Estimation**

Uncertainty plays also an important role when we care more about the **average performance**

#### **Quantitative Estimation**

Uncertainty plays also an important role when we care more about the **average performance**

Assumption: execution times are distributed uniformly.

### **Quantitative Estimation**

Uncertainty plays also an important role when we care more about the **average performance**

Assumption: execution times are distributed uniformly.

With simulation we get more quantitative information:

Analysis based on deterministic values (lower and upper) might give incorrect bounds on the global response time.

- Analysis based on deterministic values (lower and upper) might give incorrect bounds on the global response time.

- Timed automata reachability analysis gives us correct bounds but no quantitative information.

- Analysis based on deterministic values (lower and upper) might give incorrect bounds on the global response time.

- Timed automata reachability analysis gives us correct bounds but no quantitative information.

- Stochastic simulation does not catch tight bounds but gives more quantitative information about average performance.

- Analysis based on deterministic values (lower and upper) might give incorrect bounds on the global response time.

- Timed automata reachability analysis gives us correct bounds but no quantitative information.

- Stochastic simulation does not catch tight bounds but gives more quantitative information about average performance.

Introduction Overview DESPEX DeSpEx: The Too Conclusion Case Study

# Introduction

Context A motivating example

## DESPEX

### Overview DeSpEx: The Tool

Case Study

Conclusion

Introduction Overview DESPEX DeSpEx: The Too Conclusion Case Study

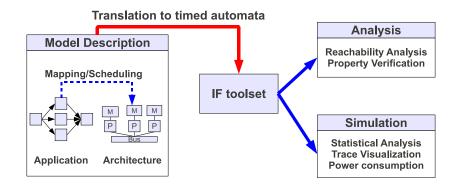

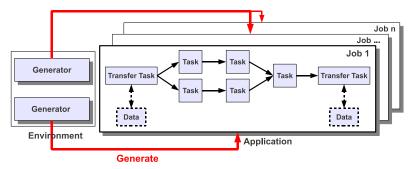

### **DeSpEx** A framework for high level modeling and analysis

- Provide HW/SW designers with a framework for rapid design space exploration

- High level language for model description

- Formal semantics provided by timed automata

- Performance evaluation using formal methods and stochastic simulation

Introduction Overview DESPEX DeSpEx: The To Conclusion Case Study

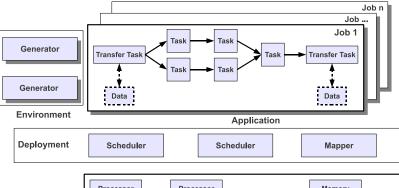

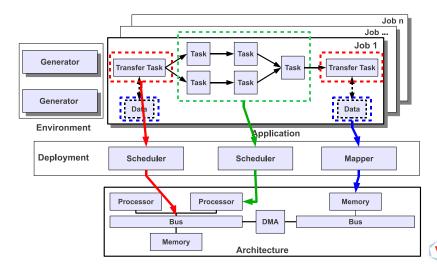

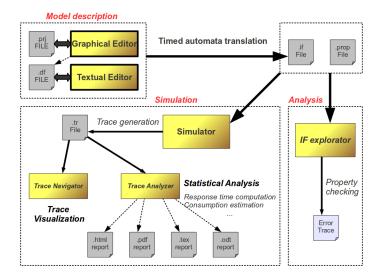

#### **Framework Overview**

Introduction Overview DESPEX DeSpEx: The Tool Conclusion Case Study

Application

Introduction Overview DESPEX DeSpEx: The Tool Conclusion Case Study

Introduction Overview DESPEX DeSpEx: The Tool Conclusion Case Study

Introduction Overview DESPEX DeSpEx: The Tool Conclusion Case Study

## **Evaluation**

The aim of this modeling framework is to provide design space exploration for performance evaluation

### **Evaluation**

- The aim of this modeling framework is to provide design space exploration for performance evaluation

- For each component we generate a corresponding timed automaton model

## **Evaluation**

- The aim of this modeling framework is to provide design space exploration for performance evaluation

- For each component we generate a corresponding timed automaton model

- The composition of all automata yields a global timed automaton which captures the semantics of the system

## **Evaluation**

- The aim of this modeling framework is to provide design space exploration for performance evaluation

- For each component we generate a corresponding timed automaton model

- The composition of all automata yields a global timed automaton which captures the semantics of the system

- All our analysis methods are based on a unified semantic model provided by timed automata

### Introduction

Context A motivating example

## DESPEX

Overview DeSpEx: The Tool Case Study

Conclusion

## **Tool Overview**

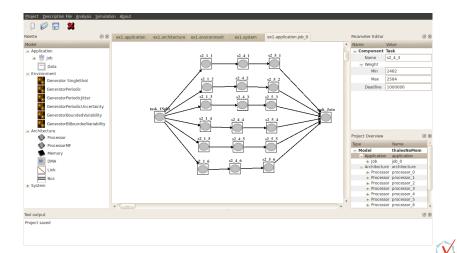

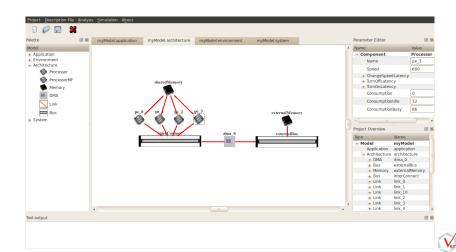

### **DeSpEx: Graphical Model Editor**

#### **DeSpEx: Graphical Model Editor** Architecture inspired by P2012 platform

#### **DeSpEx: Graphical Model Editor** Architecture inspired by Cell platform

Project Description File Analysis Simulation About 🥟 🕞 🗶 Parameter Editor 12 X Palette 88 myModel.application myModel.architecture mvModel.environment mvModel.system Value + Application - Component Processor + Environment Name pe 3 + Architecture 600 Speed + System + ChangeSpeedLatency + TurnOffLatency + TurnOnLatency mem\_1 mem 2 Consumption ConsumptionIdle ConsumptionBusy externalMemory Project Overview Type Name - Model myModel application Application + Architecture architecture Environment environment System system Tool output (7 X

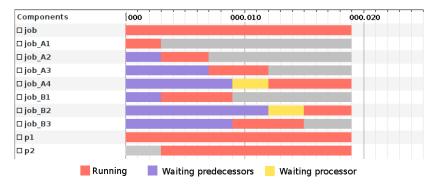

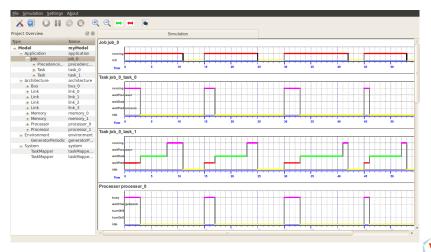

#### **DeSpEx: Simulation and Trace Visualization**

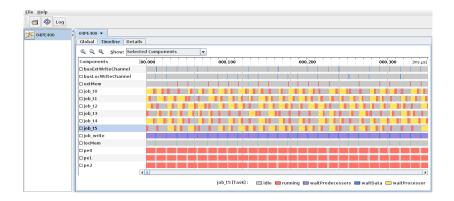

## **DeSpEx: Trace Visualization (Gantt Chart)**

# Reachability Analysis

- Check whether some properties are satisfied or not

- In case of property violation generates an error trace, viewable with the GUI

# Reachability Analysis

- Check whether some properties are satisfied or not

- In case of property violation generates an error trace, viewable with the GUI

# **Stochastic Simulation**

- Depending on the size of the model it may be difficult (sometimes impossible) to perform reachability analysis

- Timed automata are used to perform discrete event simulation:

- Semantic model is the same as for reachability analysis

- Randomized reachability exploration

- We restrict ourself to bounded uncertainty

**Trace Analysis**

- Stochastic simulation generates timed traces

- We can retrieve quantitative informations with trace analysis:

- Response time distribution of job

**Trace Analysis**

- Stochastic simulation generates timed traces

- We can retrieve quantitative informations with trace analysis:

- Response time distribution of job

- Power consumption estimation

### Introduction

Context A motivating example

## DESPEX

Overview DeSpEx: The Tool Case Study

## Conclusion

## Case Study Video Processing on P2012

# Goal

Demonstrate how DeSpEx can be used to solve realistic problems in design space exploration

## Case Study Video Processing on P2012

# Goal

- Demonstrate how DeSpEx can be used to solve realistic problems in design space exploration

- Quantify the performance differences between different design choices

## Case Study Video Processing on P2012

# Goal

- Demonstrate how DeSpEx can be used to solve realistic problems in design space exploration

- Quantify the performance differences between different design choices

- Represent available cost/performance trade-offs.

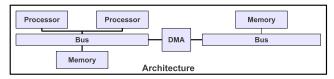

#### **Architecture Abstraction**

- P2012 is a many-core computing fabric based on multiple clusters

- We restrict our models to one cluster

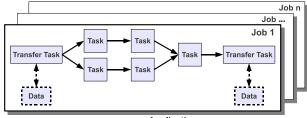

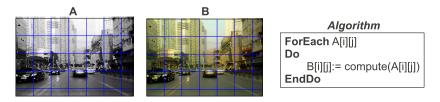

#### Video Processing on P2012 Application

- Augmented reality application called FAST (Features from Accelerated Segment Test)

- Corner detection method

- Algorithm consists in computing the detection on a chunk of an image

From an architectural point of view:

- The image resides initially in the off-chip memory

- Needs to be brought to local memory

- Then dispatched to processors for execution

### **Constraints:**

- The whole image does not fit into the local memory

- Several alternatives for its splitting and transfer to local memories

At early design stage:

- no physical platform

- no complete implementation

At early design stage:

- no physical platform

- no complete implementation

## Compare different design alternatives with DeSpEx

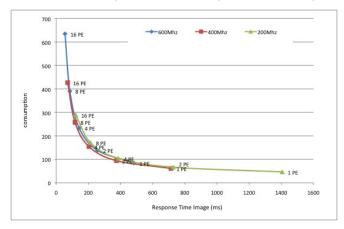

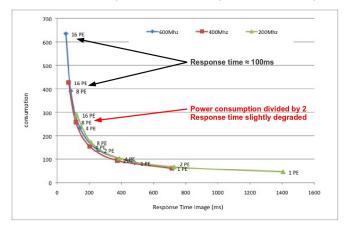

- How many processors should we use ? 1,2,4,8 or 16

- At which processor frequency? 200, 400 or 600 MHz

At early design stage:

- no physical platform

- no complete implementation

## Compare different design alternatives with DeSpEx

- How many processors should we use ? 1,2,4,8 or 16

- At which processor frequency? 200, 400 or 600 MHz

## Depends on different criteria for processing an image:

Response time

At early design stage:

- no physical platform

- no complete implementation

## Compare different design alternatives with DeSpEx

- How many processors should we use ? 1,2,4,8 or 16

- At which processor frequency? 200, 400 or 600 MHz

## Depends on different criteria for processing an image:

- Response time

- Power consumption of the platform

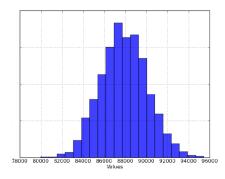

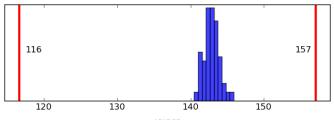

## Video Processing on P2012: Evaluation Worst-Case vs Statistics

Compare results from simulation and reachability analysis:

Response time of processing one image.

- Bands treatment

- 4 processors (600 MHz)

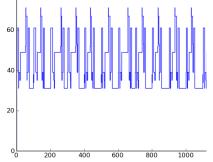

## Video Processing on P2012: Evaluation Power Consumption

We compare different configuration of the platform to get the trade-offs between response time and power consumption.

## Video Processing on P2012: Evaluation Power Consumption

We compare different configuration of the platform to get the trade-offs between response time and power consumption.

Introduction DESPEX Conclusion

## Introduction

Context A motivating example

### DESPEX

Overview DeSpEx: The Tool Case Study

## Conclusion

### **Conclusion and future work**

- We provide a tool-supported framework for Design-Space Exploration based on abstract model

- The framework and analysis techniques have been implemented into an extensible toolset: DeSpEx

### **Conclusion and future work**

- We provide a tool-supported framework for Design-Space Exploration based on abstract model

- The framework and analysis techniques have been implemented into an extensible toolset: DeSpEx

# Future work:

- Enrich the component library

- Integration with other formalism such as Synchronous Data-Flow

- Integration of a module for piecewise analytic computation of expected performance

## **Conclusion and future work**

- We provide a tool-supported framework for Design-Space Exploration based on abstract model

- The framework and analysis techniques have been implemented into an extensible toolset: DeSpEx

# Future work:

- Enrich the component library

- Integration with other formalism such as Synchronous Data-Flow

- Integration of a module for piecewise analytic computation of expected performance

## Thank you for your attention