# AMT: a Property-based Tool for Monitoring Analog Systems

Dejan Ničković Verimag

Oded Maler Verimag

# **Overview**

- Introduction

- STL/PSL Specification Language

- Analog Layer

- Temporal Layer

- Distance-based Operators

- Checking STL/PSL Properties

- Offline Marking

- Incremental Marking

- AMT Tool

- FLASH Memory Case Study

- Verification of discrete systems

- Model checking TL specs

- Central role in algorithmic verification

- Efficient algorithms for LTL, CTL, PSL etc.

- Verification of real-time systems

- Emptiness checking of timed automata

- KRONOS, UPPAAL, IF etc.

- Many variants of real-time logics

- MTL, MITL, TCTL etc.

- Only TCTL used in a real-time verification tool

- Lightweight verification

- Systems may be too complex to verify exhaustivly

- Software

- Very large digital systems

- Many real-time systems etc.

- Property monitors

- Generated automatically from the specification

- Observe individual simulation traces and check whether the property is violated

- Incomplete but more reliable method than manual visual inspection of simulation traces

- Verification of discrete systems

- Model checking TL specs

- Central role in algorithmic verification

- Efficient algorithms for LTL, CTL, PSL etc.

- Verification of real-time systems

- Emptiness checking of timed automata

- KRONOS, UPPAAL, IF etc.

- Many variants of real-time logics

- MTL, MITL, TCTL etc.

- Only TCTL used in a real-time verification tool

- Lightweight verification

- Systems may be too complex to verify exhaustivly

- Software

- Very large digital systems

- Many real-time systems etc.

- Property monitors

- Generated automatically from the specification

- Observe individual simulation traces and check whether the property is violated

- Incomplete but more reliable method than manual visual inspection of simulation traces

- Verification of discrete systems

- Model checking TL specs

- Central role in algorithmic verification

- Efficient algorithms for LTL, CTL, PSL etc.

- Verification of real-time systems

- Emptiness checking of timed automata

- KRONOS, UPPAAL, IF etc.

- Many variants of real-time logics

- MTL, MITL, TCTL etc.

- Only TCTL used in a real-time verification tool

- Lightweight verification

- Systems may be too complex to verify exhaustivly

- Software

- Very large digital systems

- Many real-time systems etc.

- Property monitors

- Generated automatically from the specification

- Observe individual simulation traces and check whether the property is violated

- Incomplete but more reliable method than manual visual inspection of simulation traces

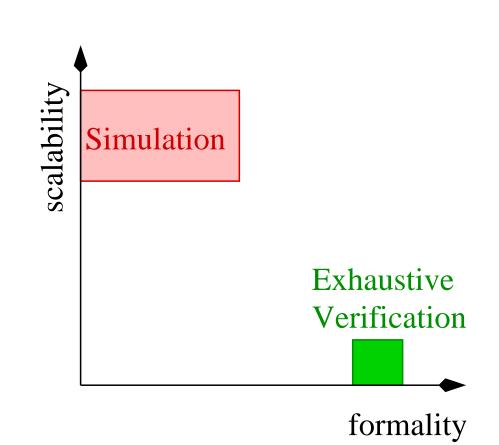

- Verification of continuous systems

- Manual inspection of simulation traces

- Dominant technique

- Requires experienced specialists

- Error prone

- Exhaustive analog verification

- Powerful formalisms such as hybrid automata

- Limited scalability

- Our approach: Property-based lightweigh verification of continuous signals

formality

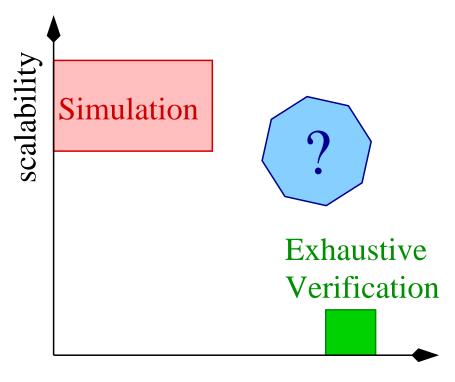

- Verification of continuous systems

- Manual inspection of simulation traces

- Dominant technique

- Requires experienced specialists

- Error prone

- Exhaustive analog verification

- Powerful formalisms such as hybrid automata

- Limited scalability

- Our approach: Property-based lightweigh verification of continuous signals

- Verification of continuous systems

- Manual inspection of simulation traces

- Dominant technique

- Requires experienced specialists

- Error prone

- Exhaustive analog verification

- Powerful formalisms such as hybrid automata

- Limited scalability

- Our approach: Property-based lightweigh verification of continuous signals

formality

# Signals

- Finite length signal  $\xi$  defined over an abstract domain  $\mathbb{D}$

- Partial function  $\xi : \mathbb{T} \to \mathbb{D}$

- Length of  $\xi$  is  $r(|\xi| = r)$

- $\xi[t] = \bot$  when  $t \ge |\xi|$

- Boolean signals:  $(\xi_b) \mathbb{D} = \mathbb{B}$

- Continuous signals:  $(\xi_a) \mathbb{D} = \mathbb{R}$

- **Restriction** of a signal  $\xi$  to length d

$$\xi' = \langle \xi \rangle_d \text{ iff } \xi'[t] = \begin{cases} \xi[t] & \text{if } t < d \\ \bot & \text{otherwise} \end{cases}$$

• Concatenation  $\xi = \xi_1 \cdot \xi_2$

$$\xi[t] = \left\{ \begin{array}{ll} \xi_1[t] & \text{if } t < r_1 \\ \xi_2[t-r_1] & \text{otherwise} \end{array} \right.$$

• *d*-suffix of a signal  $\xi$ ,  $\xi' = d \setminus \xi$

$$\xi'[t] = \xi[t+d]$$

for every  $t \in [0, |\xi| - d)$

# Signals

• Minkowski sum and difference of two sets  $P_1$  and  $P_2$  are defined as

$P_1 \oplus P_2 = \{x_1 + x_2 : x_1 \in P_1, x_2 \in P_2\}$  $P_1 \oplus P_2 = \{x_1 - x_2 : x_1 \in P_1, x_2 \in P_2\}.$

- **Projection** of the signal  $\xi$  on the dimension with domain  $\mathbb{B}$  which corresponds to the proposition p,  $\xi_p = \pi_p(\xi)$

- Likewise  $\xi_s = \pi_s(\xi)$  is the projection of the signal  $\xi$  on the dimension with domain  $\mathbb{R}$  which corresponds to the continuous variable *s*

### Signal representation

- Boolean signals:

- Non-Zeno finite length signals admit finite representation

- Sequence of adjacent intervals with value constant in each interval

- Continuous signals:

- Do not admit an exact finite representation

- But, numerical simulators produce a **finite** collection of sampling points

- The signal value at missing points in time is interpolated

- Extension of real-time temporal logic MITL with analog constructs

- PsL-like layered approach

- Analog layer: allows reasoning about continuous signals

- Temporal layer: relates the temporal behavior of input traces

- "Communication" between two layers via static abstractions

- Partitioning of the continuous state space according to the satisfaction of some inequality constraints on the continuous variables

- Targeted to be used in *lightweight* verification

- PSL-like finitary interpratation of temporal operators

- Extension of real-time temporal logic MITL with analog constructs

- PSL-like layered approach

- Analog layer: allows reasoning about continuous signals

- Temporal layer: relates the temporal behavior of input traces

- "Communication" between two layers via static abstractions

- Partitioning of the continuous state space according to the satisfaction of some inequality constraints on the continuous variables

- Targeted to be used in *lightweight* verification

- PSL-like finitary interpratation of temporal operators

- Extension of real-time temporal logic MITL with analog constructs

- PSL-like layered approach

- Analog layer: allows reasoning about continuous signals

- Temporal layer: relates the temporal behavior of input traces

- "Communication" between two layers via static abstractions

- Partitioning of the continuous state space according to the satisfaction of some inequality constraints on the continuous variables

- Targeted to be used in *lightweight* verification

- PSL-like finitary interpratation of temporal operators

- Extension of real-time temporal logic MITL with analog constructs

- PSL-like layered approach

- Analog layer: allows reasoning about continuous signals

- Temporal layer: relates the temporal behavior of input traces

- "Communication" between two layers via static abstractions

- Partitioning of the continuous state space according to the satisfaction of some inequality constraints on the continuous variables

- Targeted to be used in *lightweight* verification

- PSL-like finitary interpratation of temporal operators

# STL/PSL: Analog Layer

#### • Syntax:

$\phi :== s \mid \texttt{shift}(\phi, \texttt{k}) \mid \phi_1 \star \phi_2 \mid \phi \star \texttt{c} \mid \texttt{abs}(\phi)$

where *s* belongs to a set  $S = \{s_1, s_2, \ldots, s_n\}$  of continuous variables,  $\star \in \{+, -, \star\}$ ,  $c \in \mathbb{Q}$  and  $k \in \mathbb{Q}^+$ .

Semantics:

$$\begin{split} s[t] &= \pi_s(\xi)[t] \\ \text{shift}(\phi, \mathbf{k})[t] &= \phi[t + \mathbf{k}] \\ (\phi_1 \star \phi_2)[t] &= \phi_1[t] \star \phi_2[t] \\ (\phi \star \mathbf{c})[t] &= \phi[t] \star \mathbf{c} \\ \text{abs}(\varphi)[t] &= \begin{cases} \phi[t] & \text{if } \phi[t] \ge 0 \\ -\phi[t] & \text{otherwise} \end{cases} \end{split}$$

- Pragmatic choice of analog operators

- Based on the feedback of analog designers

- Can be naturally extended

#### • Syntax:

$\phi :== s \mid \texttt{shift}(\phi, \texttt{k}) \mid \phi_1 \star \phi_2 \mid \phi \star \texttt{c} \mid \texttt{abs}(\phi)$

where s belongs to a set  $S = \{s_1, s_2, \ldots, s_n\}$  of continuous variables,  $\star \in \{+, -, \star\}$ ,  $c \in \mathbb{Q}$  and  $k \in \mathbb{Q}^+$ .

• Semantics:

$$s[t] = \pi_s(\xi)[t]$$

shift( $\phi, \mathbf{k}$ )[ $t$ ] =  $\phi[t + \mathbf{k}]$

( $\phi_1 \star \phi_2$ )[ $t$ ] =  $\phi_1[t] \star \phi_2[t]$

( $\phi \star \mathbf{c}$ )[ $t$ ] =  $\phi[t] \star \mathbf{c}$

abs( $\varphi$ )[ $t$ ] =  $\begin{cases} \phi[t] & \text{if } \phi[t] \ge 0 \\ -\phi[t] & \text{otherwise} \end{cases}$

- Pragmatic choice of analog operators

- Based on the feedback of analog designers

- Can be naturally extended

#### • Syntax:

$\phi :== s \mid \texttt{shift}(\phi, \texttt{k}) \mid \phi_1 \star \phi_2 \mid \phi \star \texttt{c} \mid \texttt{abs}(\phi)$

where s belongs to a set  $S = \{s_1, s_2, \ldots, s_n\}$  of continuous variables,  $\star \in \{+, -, \star\}$ ,  $c \in \mathbb{Q}$  and  $k \in \mathbb{Q}^+$ .

• Semantics:

$$\begin{split} s[t] &= \pi_s(\xi)[t] \\ \text{shift}(\phi, \mathbf{k})[t] &= \phi[t + \mathbf{k}] \\ (\phi_1 \star \phi_2)[t] &= \phi_1[t] \star \phi_2[t] \\ (\phi \star \mathbf{c})[t] &= \phi[t] \star \mathbf{c} \\ \text{abs}(\varphi)[t] &= \begin{cases} \phi[t] & \text{if } \phi[t] \ge 0 \\ -\phi[t] & \text{otherwise} \end{cases} \end{split}$$

- Pragmatic choice of analog operators

- Based on the feedback of analog designers

- Can be naturally extended

# STL/PSL: Temporal Layer

### • Syntax:

$$\begin{split} \varphi :=&= p \mid \phi \circ c \mid \text{not } \varphi \mid \varphi_1 \text{ or } \varphi_2 \mid \text{eventually! } \varphi \mid \\ \text{eventually! [a:b] } \varphi \mid \text{eventually[a:b] } \varphi \mid \\ \varphi_1 \text{ until! } \varphi_2 \mid \varphi_1 \text{ until! [a:b] } \varphi_2 \end{split}$$

where p belongs to a set  $P = \{p_1, p_2, \dots, p_n\}$  of propositional variables, a,b,c  $\in Q$  and  $\circ \in \{>, >=, <, <=\}$ .

• Semantics: The satisfaction relation  $(\xi, t) \models \varphi$ , indicating that signal  $\xi$  satisfies  $\varphi$  at time t is defined inductively as follows:

| $(\xi,t) \models \texttt{eventually!} \varphi$       | iff | _ |

|------------------------------------------------------|-----|---|

| $(\xi, t) \models \texttt{eventually![a:b]} \varphi$ | iff | _ |

| $(\xi,t)\models arphi_1$ until! $arphi_2$            | iff | _ |

|                                                      |     |   |

$$(\xi,t) \models \varphi_1 \text{ until![a:b]} \varphi_2$$

$$\begin{array}{ll} \mathrm{iff} & \exists t' \geq t \; \mathrm{st} \; t' < |\xi| \; \mathrm{and} \; (\xi,t') \models \varphi \\ \mathrm{iff} & \exists t' \in t \oplus [a,b] \; \mathrm{st} \; t' < |\xi| \; \mathrm{and} \; (\xi,t') \models \varphi \\ \mathrm{iff} & \exists t' \geq t \; \mathrm{st} \; t' < |\xi| \; \mathrm{and} \; (\xi,t') \models \varphi_2 \; \mathrm{and} \\ \forall t'' \in [t,t'] \; (\xi,t'') \models \varphi_1 \\ \mathrm{iff} & \exists t' \in t \oplus [a,b] \; \mathrm{st} \; t' < |\xi| \; \mathrm{and} \; (\xi,t') \models \varphi_2 \; \mathrm{and} \\ \forall t'' \in [t,t'] \; (\xi,t'') \models \varphi_1 \end{array}$$

# STL/PSL: Temporal Layer

### • Syntax:

```

\begin{split} \varphi :=&= p \mid \phi \circ c \mid \text{not } \varphi \mid \varphi_1 \text{ or } \varphi_2 \mid \text{eventually! } \varphi \mid \\ \text{eventually![a:b] } \varphi \mid \text{eventually[a:b] } \varphi \mid \\ \varphi_1 \text{ until! } \varphi_2 \mid \varphi_1 \text{ until![a:b] } \varphi_2 \end{split}

```

where p belongs to a set  $P = \{p_1, p_2, \dots, p_n\}$  of propositional variables, a, b, c  $\in Q$  and  $\circ \in \{>, >=, <, <=\}$ .

• Semantics: The satisfaction relation  $(\xi, t) \models \varphi$ , indicating that signal  $\xi$  satisfies  $\varphi$  at time t is defined inductively as follows:

| $(\xi,t) \models eventually! \varphi$                     | iff | $\exists t' \geq t \; \texttt{st} \; t' <  \xi  \; \texttt{and} \; (\xi,t') \models arphi$                                  |

|-----------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------|

| $(\xi, t) \models eventually![a:b] \varphi$               | iff | $\exists t' \in t \oplus [a,b] \text{ st } t' <  \xi  \text{ and } (\xi,t') \models \varphi$                                |

| $(\xi,t)\models arphi_1$ until! $arphi_2$                 | iff | $\exists t' \geq t \text{ st } t' <  \xi  \text{ and } (\xi, t') \models \varphi_2 \text{ and } $                           |

|                                                           |     | $\forall t^{\prime\prime} \in [t, t^{\prime}] \ (\xi, t^{\prime\prime}) \models \varphi_1$                                  |

| $(\xi,t) \models \varphi_1 \text{ until![a:b]} \varphi_2$ | iff | $\exists t' \in t \oplus [a, b] \text{ st } t' <  \xi  \text{ and } (\xi, t') \models \varphi_2 \text{ and } \xi' \in \xi'$ |

iff

$$\exists t' \in t \oplus [a, b] \text{ st } t' < |\xi| \text{ and } (\xi, t') \models \varphi_2 \text{ and} \\ \forall t'' \in [t, t'] \ (\xi, t'') \models \varphi_1$$

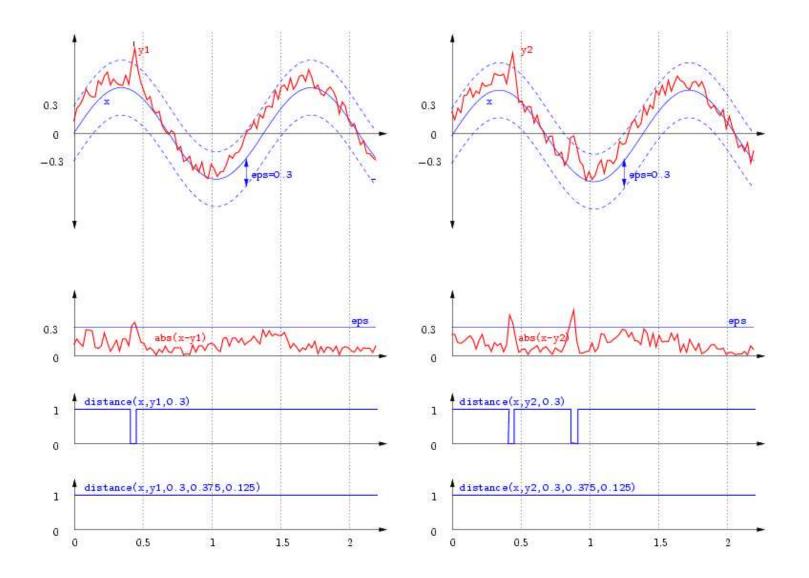

## STL/PSL: Distance-based Operators

- Motivation: Enrich STL/PSL with metric properties

- Compare waveforms with some reference signal that specifies a desired behavior

- Distance function (metric)

- Quantifies numerically the resemblance of two signals

### STL/PSL: Distance-based Operators Example

# Checking STL/PSL Properties

- Marking: a procedure that determines the truth values of each subformula of an STL/PSL specification at every time instant t

- Doubly-recursive procedure, on time and the structure of the formula

- Two algorithms for checking STL/PSL properties:

- Offline marking: input is fully available

- Incremental marking: input is dynamically observed

- Based on [MalerN04]

# Checking STL/PSL Properties

- Marking: a procedure that determines the truth values of each subformula of an STL/PSL specification at every time instant t

- Doubly-recursive procedure, on time and the structure of the formula

- Two algorithms for checking STL/PSL properties:

- Offline marking: input is fully available

- Incremental marking: input is dynamically observed

- Based on [MalerN04]

# Checking STL/PSL Properties

- Marking: a procedure that determines the truth values of each subformula of an STL/PSL specification at every time instant t

- Doubly-recursive procedure, on time and the structure of the formula

- Two algorithms for checking STL/PSL properties:

- Offline marking: input is fully available

- Incremental marking: input is dynamically observed

- Based on [MalerN04]

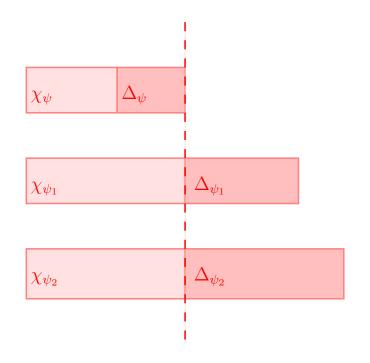

# **Offline Marking**

```

\begin{array}{c|c} \text{input} : & \mathsf{STL/PSL} \text{ Temporal Formula } \varphi \text{ and signal } \xi \\ \text{switch } \varphi \text{ do} \\ & \begin{array}{c} \mathbf{case} \ p \\ & | \ \chi_{\varphi} := \pi_p(\xi); \\ \text{end} \\ & \mathbf{case} \ \mathsf{OP}_2(\varphi_1, \varphi_2) \\ & | \ \mathsf{OFFLINE} \ (\varphi_1, \varphi_2); \\ & \chi_{\varphi} := \mathsf{COMBINE}(\mathsf{OP}_2, \chi_{\varphi_1}, \chi_{\varphi_2})); \\ & \text{end} \\ \end{array}

```

- Inputs:

- Multidimentional signal  $\xi$

- STL/PSL specification  $\varphi$

- Compute, from **bottom-up**, a signal  $\chi_{\psi}(\xi)$  for each subformila  $\psi$  of  $\phi$

- COMBINE computes from input signals a new signal based on the specific operation

# **Offline Marking**

```

\begin{array}{c|c} \text{input} : & \mathsf{STL/PSL} \text{ Temporal Formula } \varphi \text{ and signal } \xi \\ \text{switch } \varphi \text{ do} \\ & \begin{array}{c} \mathbf{case} \ p \\ & | \ \chi_{\varphi} := \pi_p(\xi); \\ \text{end} \\ & \begin{array}{c} \mathbf{case} \ \mathsf{OP}_2(\varphi_1, \varphi_2); \\ & | \ \mathsf{OFFLINE} \ (\varphi_1, \varphi_2); \\ & \chi_{\varphi} := \mathsf{COMBINE}(\mathsf{OP}_2, \chi_{\varphi_1}, \chi_{\varphi_2})); \\ & \begin{array}{c} \mathbf{end} \\ \end{array} \\ \end{array} \\ \\ \text{end} \\ \end{array} \\ \end{array}

```

- Inputs:

- Multidimentional signal  $\xi$

- STL/PSL specification  $\varphi$

- Compute, from **bottom-up**, a signal  $\chi_{\psi}(\xi)$  for each subformila  $\psi$  of  $\phi$

- COMBINE computes from input signals a new signal based on the specific operation

# **Offline Marking**

```

\begin{array}{c|c} \text{input} : & \mathsf{STL/PSL} \text{ Temporal Formula } \varphi \text{ and signal } \xi \\ \text{switch } \varphi \text{ do} \\ & \begin{array}{c} \mathbf{case} \ p \\ & | \ \chi_{\varphi} := \pi_p(\xi); \\ \text{end} \\ \mathbf{case} \ \mathsf{OP}_2(\varphi_1, \varphi_2) \\ & | \ \mathsf{OFFLINE} \ (\varphi_1, \varphi_2); \\ & \chi_{\varphi} := \mathsf{COMBINE}(\mathsf{OP}_2, \chi_{\varphi_1}, \chi_{\varphi_2})); \\ \text{end} \\ \text{end} \\ \end{array}

```

- Inputs:

- Multidimentional signal  $\xi$

- STL/PSL specification  $\varphi$

- Compute, from **bottom-up**, a signal  $\chi_{\psi}(\xi)$  for each subformila  $\psi$  of  $\phi$

- COMBINE computes from input signals a new signal based on the specific operation

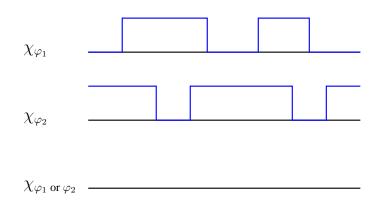

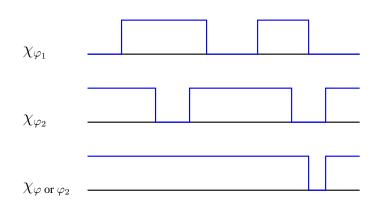

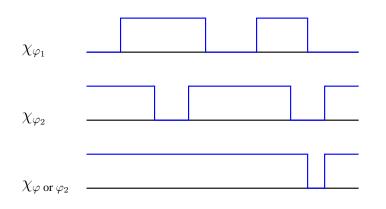

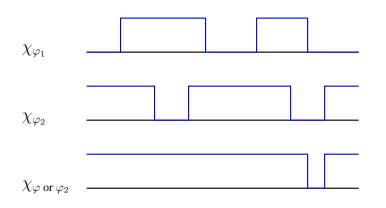

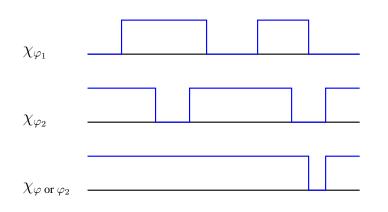

### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub>

so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

- For every positive interval  $I \in \chi_{\varphi_1}$

- Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in  $\chi_{\varphi}$

### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub> so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

- For every positive interval  $I \in \chi_{\varphi_1}$

- Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in  $\chi_{\varphi}$

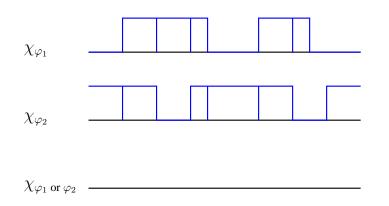

### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub> so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

- For every positive interval  $I \in \chi_{\varphi_1}$

- Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in  $\chi_{\varphi}$

### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub> so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

- For every positive interval  $I \in \chi_{\varphi_1}$

- Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in  $\chi_{\varphi}$

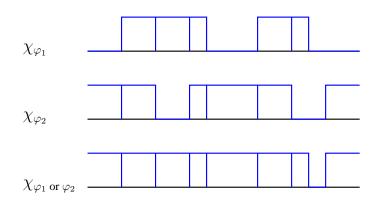

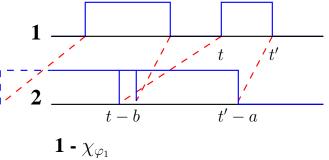

#### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub> so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

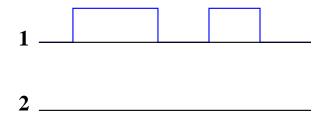

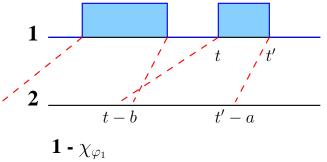

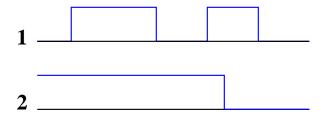

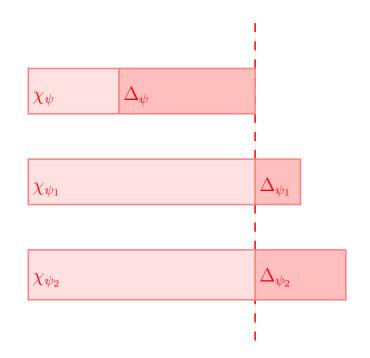

- Bounded Eventually

- For every positive interval  $I \in \chi_{\varphi_1}$

- ♦ Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in  $\chi_{\varphi}$

1 -  $\chi_{\varphi_1}$ 2 - eventually![a,b]  $\chi_{\varphi_1}$

### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub> so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

- Bounded Eventually

- For every positive interval  $I \in \chi_{\varphi_1}$

- Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in  $\chi_{\varphi}$

<sup>2 -</sup> eventually![a,b]  $\chi_{\varphi_1}$

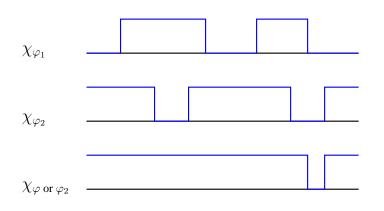

### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub> so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

- Bounded Eventually

- For every positive interval  $I \in \chi_{\varphi_1}$

- Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in  $\chi_{\varphi}$

**2** - eventually![a,b]  $\chi_{\varphi_1}$

### Disjunction

- Refine the intervals of χ<sub>φ1</sub> and χ<sub>φ2</sub> so that the mutual values of both signals become uniform in every interval

- Compute the disjunction intervalwise

- Merge the adjacent intervals having the same value

- Bounded Eventually

- For every positive interval  $I \in \chi_{\varphi_1}$

- Compute its back shifting  $I [a, b] \cap \mathbb{T}$

- Merge the overlapping intervals in *χ*<sub>φ</sub>

1 -  $\chi_{\varphi_1}$ 2 - eventually![a,b]  $\chi_{\varphi_1}$

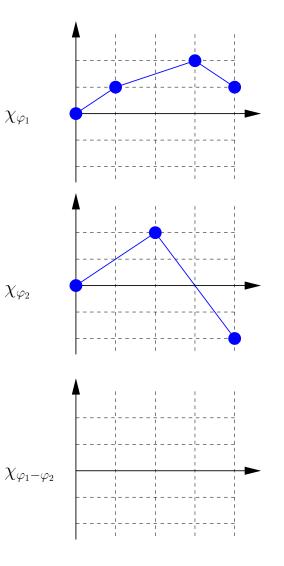

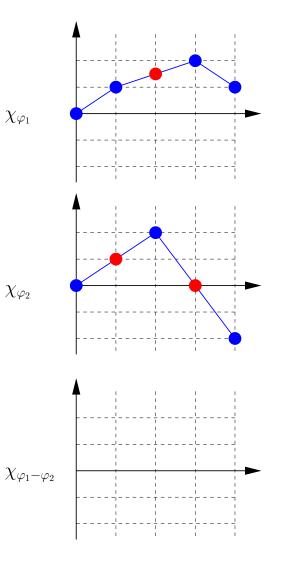

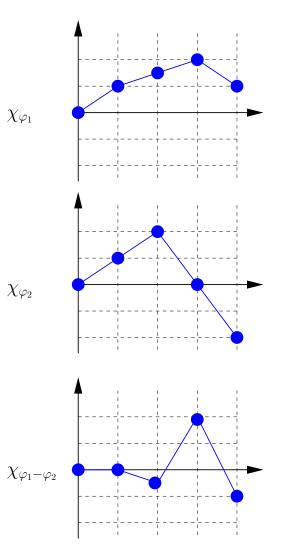

# COMBINE: Arithmetic Operations

- Pointwise arithmetic operation on two signals

- Take the union of their sampling points

- Extend each signal to the new points by interpolation

- Apply the operation on each pair of sampling points

# COMBINE: Arithmetic Operations

- Pointwise arithmetic operation on two signals

- Take the union of their sampling points

- Extend each signal to the new points by interpolation

- Apply the operation on each pair of sampling points

# COMBINE: Arithmetic Operations

- Pointwise arithmetic operation on two signals

- Take the union of their sampling points

- Extend each signal to the new points by interpolation

- Apply the operation on each pair of sampling points

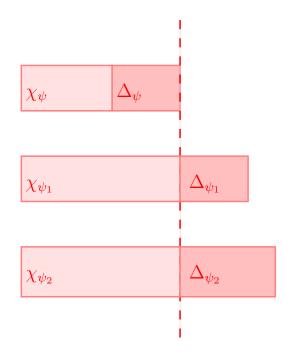

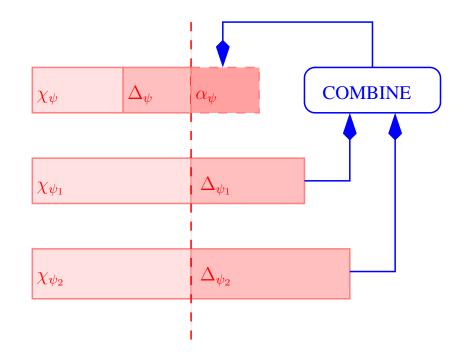

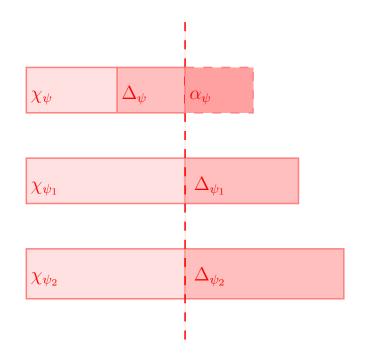

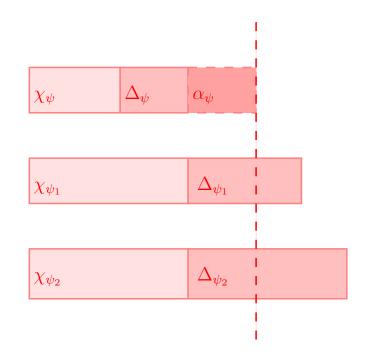

**input** : STL/PSL Temporal Formula  $\varphi$  and increment  $\Delta_{\xi}$ switch  $\varphi$  do case p $\Delta_{\varphi} := \Delta_{\varphi} \cdot \pi_p(\Delta_{\xi});$ end case  $\mathsf{OP}_2(\varphi_1,\varphi_2)$ INCREMENTAL  $(\varphi_1, \varphi_2);$  $\alpha_{\varphi} := \mathsf{COMBINE}(\mathsf{OP}_2, \chi_{\varphi_1}, \chi_{\varphi_2}));$  $d := |\alpha_{\varphi}|;$  $\Delta_{\varphi} := \Delta_{\varphi} \cdot \alpha_{\varphi} ;$  $\chi_{\varphi_1}^{\varphi} := \chi_{\varphi_1}^{\varphi} \cdot \langle \Delta_{\varphi_1} \rangle_d ;$   $\Delta_{\varphi_1}^{\varphi_1} := d \backslash \Delta_{\varphi_1}^{\varphi} ;$   $\chi_{\varphi_2}^{\varphi_2} := \chi_{\varphi_2}^{\varphi} \cdot \langle \Delta_{\varphi_2} \rangle_d ;$   $\Delta_{\varphi_2}^{\varphi_2} := d \backslash \Delta_{\varphi_2}^{\varphi}$ end end

**input** : STL/PSL Temporal Formula  $\varphi$  and increment  $\Delta_{\xi}$ switch  $\varphi$  do case p $\Delta_{\varphi} := \Delta_{\varphi} \cdot \pi_p(\Delta_{\xi});$ end case  $\mathsf{OP}_2(\varphi_1,\varphi_2)$ INCREMENTAL  $(\varphi_1, \varphi_2);$  $\alpha_{\varphi} := \mathsf{COMBINE}(\mathsf{OP}_2, \chi_{\varphi_1}, \chi_{\varphi_2}));$  $d := |\alpha_{\varphi}|;$  $\Delta_{\varphi} := \Delta_{\varphi} \cdot \alpha_{\varphi} ;$  $\chi_{\varphi_1}^{\varphi} := \chi_{\varphi_1}^{\varphi} \cdot \langle \Delta_{\varphi_1} \rangle_d ;$   $\Delta_{\varphi_1}^{\varphi_1} := d \backslash \Delta_{\varphi_1}^{\varphi} ;$   $\chi_{\varphi_2}^{\varphi_2} := \chi_{\varphi_2}^{\varphi} \cdot \langle \Delta_{\varphi_2} \rangle_d ;$   $\Delta_{\varphi_2}^{\varphi_2} := d \backslash \Delta_{\varphi_2}^{\varphi}$ end end

- Advantages of the incremental algorithm

- Often more memory efficient

- Determined parts of the signal may be discarded

- Early detection of errors

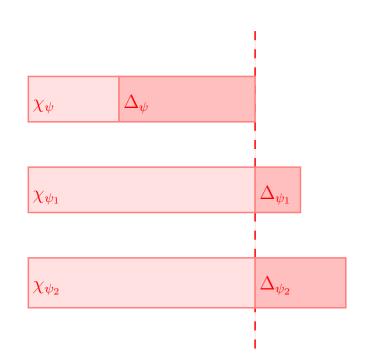

- Stand alone tool for lightweight verification of properties on continuous signals

Inputs:

- STL/PSL specification

- Input signals (Boolan or continuous)

- From a file (**raw**, **vcd** and **out** format)

- Dynamic inputs through TCP/IP packets

- **Property evaluation:**

- Offline

- Incremental

- Visual evaluation of results

- Stand alone tool for lightweight verification of properties on continuous signals

- Inputs:

- STL/PSL specification

- Input signals (Boolan or continuous)

- From a file (**raw**, **vcd** and **out** format)

- Dynamic inputs through TCP/IP packets

- **Property evaluation:**

- Offline

- Incremental

- Visual evaluation of results

- Stand alone tool for lightweight verification of properties on continuous signals

- Inputs:

- ♦ STL/PSL specification

- Input signals (Boolan or continuous)

- From a file (**raw**, **vcd** and **out** format)

- Dynamic inputs through TCP/IP packets

- Property evaluation:

- Offline

- Incremental

- Visual evaluation of results

- Stand alone tool for lightweight verification of properties on continuous signals

- Inputs:

- ♦ STL/PSL specification

- Input signals (Boolan or continuous)

- From a file (**raw**, **vcd** and **out** format)

- Dynamic inputs through TCP/IP packets

- Property evaluation:

- Offline

- Incremental

- Visual evaluation of results

#### AMT Tool: Main Window

|      | 8-        | ***         |   |   |   |   |      |    |       |

|------|-----------|-------------|---|---|---|---|------|----|-------|

|      |           |             |   |   |   |   |      |    | 1.    |

|      |           |             |   |   |   |   |      |    |       |

|      | 181 -     |             |   |   |   |   |      |    |       |

|      | -         |             |   |   |   |   |      |    |       |

|      |           |             |   |   |   |   |      |    | -1-12 |

|      | -         |             |   | - |   |   |      |    |       |

| n fi | -         |             |   |   |   | 1 |      |    |       |

|      | I LEL     | · · · · · · | - |   | - |   |      | 38 |       |

| 1    |           |             |   |   |   |   |      |    |       |

|      | CON-COLOR |             |   |   | - |   | din. |    |       |

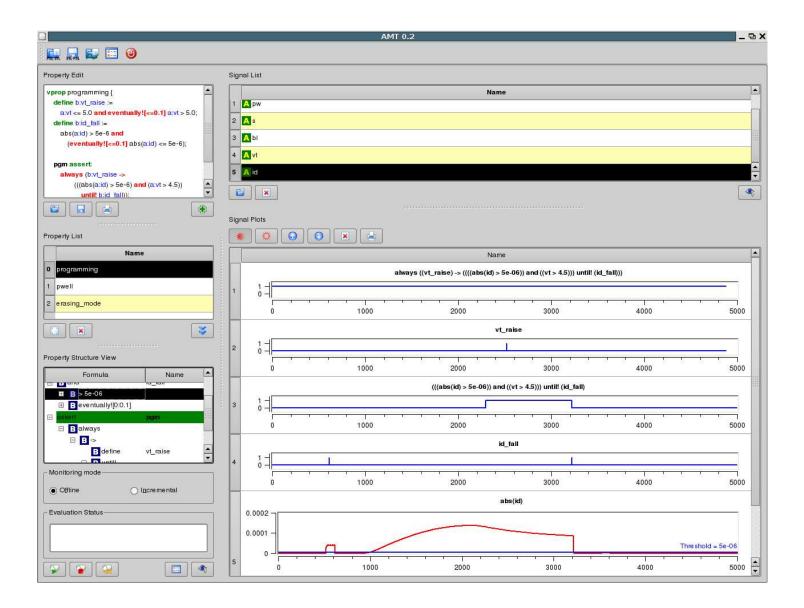

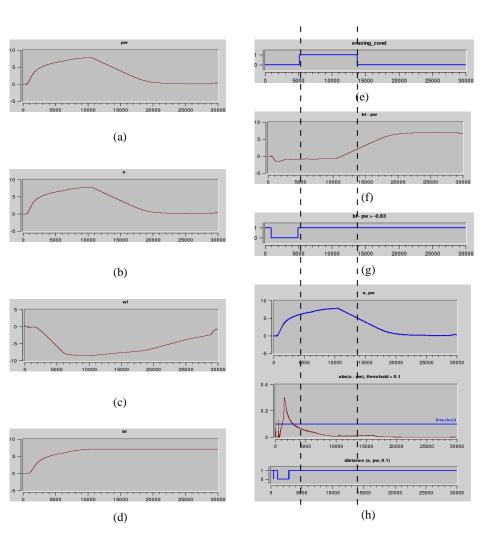

- Provided by STM Italy

- Why Flash memory?

- Analog circuit that implements digital behavior

- Good connection between analog and digital worlds

- Different modes

- Programming, reading, erasing, etc.

- Characteristic signals

- bl: bit line terminal

- **pw**: p-well terminal

- ♦ wl: word line

- s: source terminal

- vt: threshold voltage of cell

- id: drain current of cell

- Correct functioning in a given mode determined by the behavior of the characteristic signals

- 5 properties specifying the correct behavior

| 1 1 |            |  |

|-----|------------|--|

|     |            |  |

|     |            |  |

|     | 210 220 23 |  |

|     |            |  |

- Provided by STM Italy

- Why Flash memory?

- Analog circuit that implements digital behavior

- Good connection between analog and digital worlds

- Different modes

- Programming, reading, erasing, etc.

- Characteristic signals

- bl: bit line terminal

- pw: p-well terminal

- ♦ wl: word line

- s: source terminal

- vt: threshold voltage of cell

- id: drain current of cell

- Correct functioning in a given mode determined by the behavior of the characteristic signals

- 5 properties specifying the correct behavior

|   | 8-        | ***         |      |   |   |   |      |    |       |

|---|-----------|-------------|------|---|---|---|------|----|-------|

|   |           |             |      |   |   |   |      |    | 1.    |

|   |           |             |      |   |   |   |      |    |       |

|   | 181 -     |             |      |   |   |   |      |    |       |

|   | -         |             |      |   |   |   |      |    |       |

|   |           |             |      |   |   |   |      |    | -1-12 |

|   | -         |             |      | - |   |   |      |    |       |

|   | -         |             |      |   |   | 1 |      |    |       |

|   | I LEL     | · · · · · · | - 10 |   | - |   |      | 38 |       |

| 1 |           |             |      |   |   |   |      |    |       |

|   | CON-COLOR |             |      |   | - |   | din. |    |       |

- Provided by STM Italy

- Why Flash memory?

- Analog circuit that implements digital behavior

- Good connection between analog and digital worlds

- Different modes

- Programming, reading, erasing, etc.

- Characteristic signals

- bl: bit line terminal

- **pw**: p-well terminal

- wl: word line

- s: source terminal

- vt: threshold voltage of cell

- id: drain current of cell

- Correct functioning in a given mode determined by the behavior of the characteristic signals

- 5 properties specifying the correct behavior

|     | ĘЩ |            |          |    |                  |   |           |    |      |

|-----|----|------------|----------|----|------------------|---|-----------|----|------|

|     |    |            |          |    |                  |   |           |    |      |

|     |    |            |          |    |                  |   |           |    |      |

|     |    |            |          |    | 1                |   |           |    |      |

|     |    |            |          |    | -                |   |           |    | -1-3 |

| T N |    |            |          |    |                  |   |           |    | 11   |

|     |    |            |          |    |                  |   |           |    |      |

| N   |    |            | 60<br>67 | 48 |                  |   | 8<br>- 20 | i. |      |

|     |    | CONTRACT D |          |    | and an inclusion | - | -         | -  | <br> |

- Provided by STM Italy

- Why Flash memory?

- Analog circuit that implements digital behavior

- Good connection between analog and digital worlds

- Different modes

- Programming, reading, erasing, etc.

- Characteristic signals

- bl: bit line terminal

- **pw**: p-well terminal

- wl: word line

- s: source terminal

- vt: threshold voltage of cell

- id: drain current of cell

- Correct functioning in a given mode determined by the behavior of the characteristic signals

- 5 properties specifying the correct behavior

|     | ĘЩ |             |          |    |              |   |           |    |      |

|-----|----|-------------|----------|----|--------------|---|-----------|----|------|

|     |    |             |          |    |              |   |           |    |      |

|     |    |             |          |    |              |   |           |    |      |

|     |    |             |          |    | 1            |   |           |    |      |

|     |    |             |          |    | -            |   |           |    | -1-3 |

| T N |    |             |          |    |              |   |           |    | 11   |

|     |    |             |          |    | -            |   |           |    |      |

| N   |    |             | 60<br>67 | 48 |              |   | 8<br>- 20 | i. |      |

|     |    | CONTRACT OF |          |    | and an owner | - | -         | -  |      |

- Provided by STM Italy

- Why Flash memory?

- Analog circuit that implements digital behavior

- Good connection between analog and digital worlds

- Different modes

- Programming, reading, erasing, etc.

- Characteristic signals

- bl: bit line terminal

- **pw**: p-well terminal

- wl: word line

- s: source terminal

- vt: threshold voltage of cell

- id: drain current of cell

- Correct functioning in a given mode determined by the behavior of the characteristic signals

- 5 properties specifying the correct behavior

#### Case Study Example: Erasing Property

## **Tool Evaluation**

| name | pgm sim<br># intervals | erase sim<br># intervals |

|------|------------------------|--------------------------|

| wl   | 34829                  | 283624                   |

| pw   | 25478                  | 283037                   |

| S    | 33433                  | 282507                   |

| bl   | 32471                  | 139511                   |

| id   | 375                    | n/a                      |

Table 1: Input Size

### **Tool Evaluation**

| name | pgm sim<br># intervals | erase sim<br># intervals |

|------|------------------------|--------------------------|

| wl   | 34829                  | 283624                   |

| pw   | 25478                  | 283037                   |

| S    | 33433                  | 282507                   |

| bl   | 32471                  | 139511                   |

| id   | 375                    | n/a                      |

| property     | time (s) | # intervals |

|--------------|----------|-------------|

| programming1 | 0.14     | 99715       |

| programming2 | 0.42     | 405907      |

| p-well       | 0.12     | 89071       |

| decay        | 0.50     | 594709      |

| erasing      | 2.35     | 2968578     |

Table 1: Input Size

Table 2: Offline Algorithm Evaluation

### **Tool Evaluation**

| name | pgm sim<br># intervals | erase sim<br># intervals |

|------|------------------------|--------------------------|

| wl   | 34829                  | 283624                   |

| pw   | 25478                  | 283037                   |

| S    | 33433                  | 282507                   |

| bl   | 32471                  | 139511                   |

| id   | 375                    | n/a                      |

| property     | time (s) | # intervals |

|--------------|----------|-------------|

| programming1 | 0.14     | 99715       |

| programming2 | 0.42     | 405907      |

| p-well       | 0.12     | 89071       |

| decay        | 0.50     | 594709      |

| erasing      | 2.35     | 2968578     |

Table 1: Input Size

Table 2: Offline Algorithm Evaluation

|              | Offline               | Incremental                |           |

|--------------|-----------------------|----------------------------|-----------|

| Property     | t = total # intervals | m = max # active intervals | m/t * 100 |

| programming1 | 99715                 | 65700                      | 65.9      |

| programming2 | 594709                | 242528                     | 40.8      |

| p-well       | 89071                 | 8                          | 0.01      |

| decay        | 594709                | 279782                     | 47.1      |

Table 3: Offline/Incremental Space Requirement Comparison

## Conclusion

#### • Main contributions:

- AMT tool that monitors temporal properties of continuous signals

- Description of properties in STL/PSL specification language

- Offline and incremental algorithms

- Integration with numerical simulations via simulation dump files or TCP/IP link

- FLASH memory case study

- Validates the tool and the approach

- Shows the automation and efficiency of monitoring continuous signals

## Conclusion

#### • Main contributions:

- AMT tool that monitors temporal properties of continuous signals

- Description of properties in STL/PSL specification language

- Offline and incremental algorithms

- Integration with numerical simulations via simulation dump files or TCP/IP link

- FLASH memory case study

- Validates the tool and the approach

- Shows the automation and efficiency of monitoring continuous signals