# Synchronous Programming of Reactive Systems

Nicolas Halbwachs

1993

## Contents

| Li | st of                 | figures                              | ix   |

|----|-----------------------|--------------------------------------|------|

| Li | st of                 | tables                               | x    |

| Fe | orewo                 | ord                                  | xi   |

|    | List                  | of contacts concerning each language | xiii |

|    |                       | lanation of acronyms                 |      |

| 1  | Inti                  | roduction                            | 1    |

|    | 1.1                   | Reactive systems                     | 1    |

|    | 1.2                   | Classical approaches                 | 3    |

|    | 1.3                   | The synchronous approach             | 5    |

|    | 1.4                   | Complex systems                      | 6    |

|    | 1.5                   | Summary of this book                 | 7    |

| Ι  | For                   | ır Synchronous Languages             | 9    |

| 2  | $\mathrm{Th}\epsilon$ | e imperative language Esterel        | 11   |

|    | 2.1                   | Introduction                         | 11   |

|    | 2.2                   | Basic concepts                       | 11   |

|    | 2.3                   | Programming primitives               | 13   |

|    |                       | 2.3.1 Declarations                   | 14   |

|    |                       | 2.3.2 Expressions                    | 14   |

|    |                       | 2.3.3 Statements                     | 15   |

|    | 2.4                   | Programming style and first examples |      |

|    |                       | 2.4.1 Using signals as time units    |      |

|   |     | 2.4.2              | Use of broadcasting                                | 22 |

|---|-----|--------------------|----------------------------------------------------|----|

|   |     | 2.4.3              | Instantaneous dialogue                             | 23 |

|   |     | 2.4.4              | A stopwatch                                        | 25 |

|   | 2.5 | Causa              | lity problems in Esterel                           | 29 |

|   |     | 2.5.1              | Lack of behavior                                   | 29 |

|   |     | 2.5.2              | Multiple behavior                                  | 30 |

|   |     | 2.5.3              | Putting right the stopwatch                        | 31 |

|   | 2.6 | Anoth              | er example: the reflex game                        | 31 |

|   |     | 2.6.1              | Specifications                                     | 31 |

|   |     | 2.6.2              | Interface                                          | 32 |

|   |     | 2.6.3              | Computation of the average reflex time             | 33 |

|   |     | 2.6.4              | The program body                                   | 34 |

| 3 | Gra | phic f             | ormalisms: the language Argos                      | 39 |

|   | 3.1 |                    | nata and operators                                 | 40 |

|   |     | 3.1.1              | Simple automata                                    | 40 |

|   |     | 3.1.2              | Argos operators                                    | 41 |

|   | 3.2 | Causa              | lity problems                                      | 45 |

|   | 3.3 |                    | amming style                                       | 46 |

|   |     | $3.3.\overline{1}$ | Termination by exception                           | 47 |

|   |     | 3.3.2              | Normal termination                                 | 47 |

|   |     | 3.3.3              | Interrupt                                          | 49 |

|   | 3.4 | Exam               |                                                    | 49 |

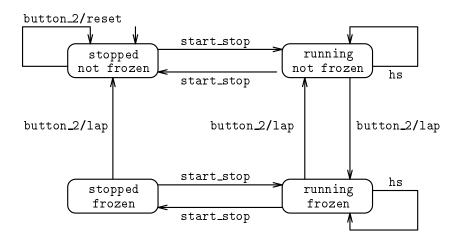

|   |     | 3.4.1              | The stopwatch                                      | 49 |

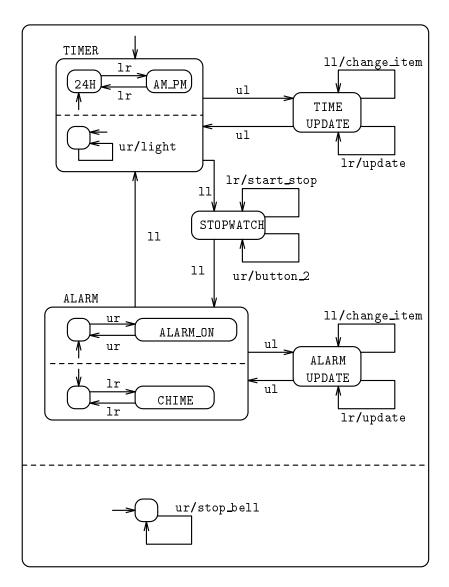

|   |     | 3.4.2              | Control logic of the digital watch                 | 49 |

| 4 | Dec | larativ            | ve languages : Lustre and Signal                   | 53 |

|   | 4.1 |                    | uction                                             | 53 |

|   | 4.2 |                    | inguage Lustre                                     | 55 |

|   |     | 4.2.1              | Flows and clocks                                   | 56 |

|   |     | 4.2.2              | Variables, equations, expressions, and assertions. | 57 |

|   |     | 4.2.3              | Program structure                                  | 60 |

|   |     | 4.2.4              | Causality in Lustre                                | 62 |

|   |     | 4.2.5              | Some examples                                      | 62 |

|   | 4.3 |                    | inguage Signal                                     | 68 |

|   |     | 4.3.1              | Signals, clocks, and operators                     | 68 |

|   |     | 139                | Program structure                                  | 71 |

| II | $\mathbf{C}_{0}$ | ompila  | ation                               | 73         |

|----|------------------|---------|-------------------------------------|------------|

| 5  | Stat             | tic ver | rifications                         | 75         |

|    | 5.1              |         | ality checking in Esterel           | 75         |

|    | 5.2              |         | ality checking in Argos             |            |

|    | 5.3              |         | checking in LUSTRE                  |            |

|    | 5.4              |         | lock calculus of Signal             |            |

| 6  | Seq              | uentia  | l code generation                   | 85         |

|    | 6.1              |         | Esterel compiler                    | 85         |

|    |                  | 6.1.1   | Principles                          |            |

|    |                  | 6.1.2   | Example                             |            |

|    |                  | 6.1.3   | Comments                            |            |

|    | 6.2              | The L   | LUSTRE compiler                     |            |

|    | _                | 6.2.1   | Node expansion                      |            |

|    |                  | 6.2.2   | Single loop                         |            |

|    |                  | 6.2.3   | Compiling LUSTRE into automata      |            |

|    | 6.3              |         | OC code and associated tools        |            |

| 7  | Dist             | tribute | ed code generation                  | 103        |

| •  | 7.1              |         | luction                             |            |

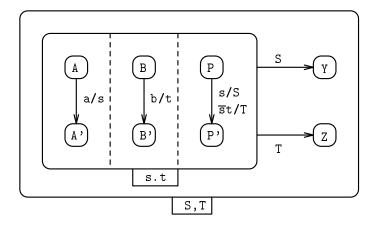

|    | 7.2              |         | distribution in SIGNAL              |            |

|    |                  | 7.2.1   | Static dependences                  |            |

|    |                  | 7.2.2   | Dynamic dependences                 |            |

|    | 7.3              |         | ode distribution                    |            |

|    | 1.5              | 7.3.1   | Code replication                    |            |

|    |                  | 7.3.2   | Placement of emission statements    |            |

|    |                  | 7.3.3   | Useless emission elimination        |            |

|    |                  | 7.3.4   | Placement of receiving statements   |            |

|    |                  | 7.3.5   | Synchronization                     |            |

|    |                  | 7.3.6   | Final processing                    |            |

|    |                  |         |                                     |            |

| 8  | Cir              | cnit oe | neration from synchronous programs  | 117        |

| 8  |                  | _       | eneration from synchronous programs | 117<br>117 |

| 8  | 8.1              | Introd  | luction                             | 117        |

| 8  |                  | Introd  |                                     | 117<br>118 |

|     |       | 8.2.3   | Translating full LUSTRE                    | <br>. 123 |

|-----|-------|---------|--------------------------------------------|-----------|

|     | 8.3   | Hardy   | vare implementation of pure Esterel        | <br>. 129 |

|     |       | 8.3.1   | Basic components                           | <br>. 129 |

|     |       | 8.3.2   | First example                              | <br>. 130 |

|     |       | 8.3.3   | Translating Parallel and Exceptions        | <br>. 133 |

|     |       |         |                                            |           |

| II. | I P   | rogra   | m Verification                             | 137       |

| 9   | Lust  | tre pro | ogram verification: the tool Lesar         | 139       |

|     | 9.1   | -       | cation of safety properties                | <br>. 140 |

|     | 9.2   | _       | ation                                      |           |

| 10  | Usir  | ng Aut  | to for Esterel program verification        | 149       |

| 11  | Con   | clusio  | n                                          | 157       |

|     | 11.1  | The co  | ommon environment of synchronous languages | <br>. 157 |

|     | 11.2  | Works   | in progress                                | <br>. 159 |

| Bi  | bliog | raphy   |                                            | 161       |

## List of Figures

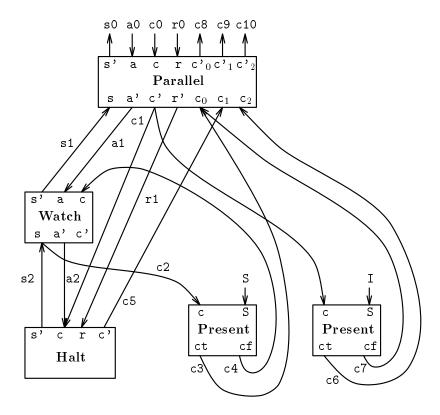

| 2.1  | The whole program of the reflex game            | 37 |

|------|-------------------------------------------------|----|

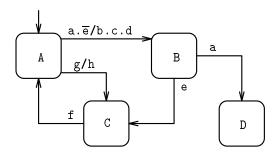

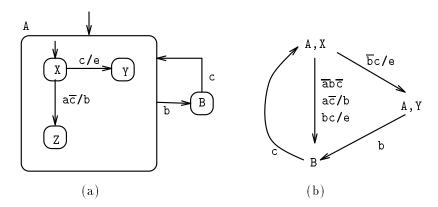

| 3.1  | An Argos automaton                              | 40 |

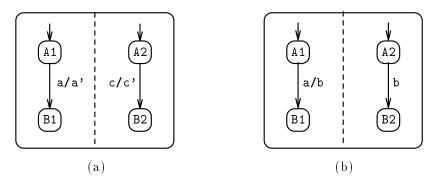

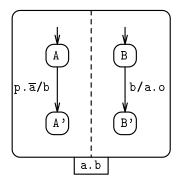

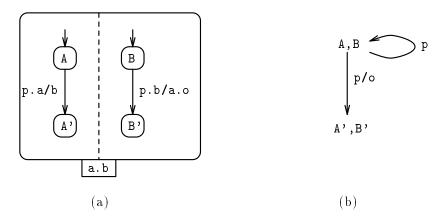

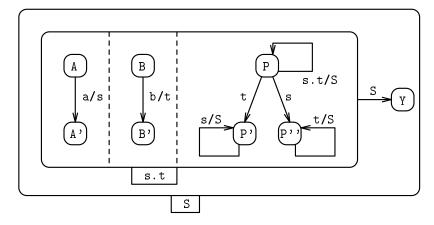

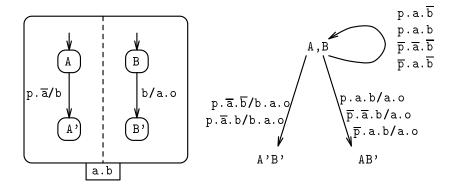

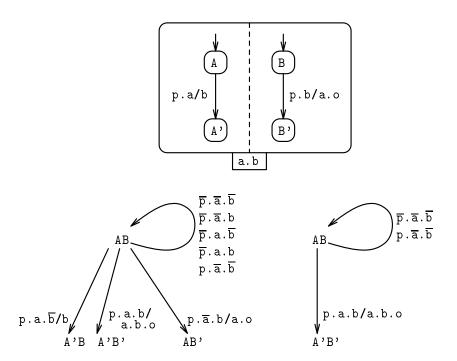

| 3.2  | Parallel composition                            | 42 |

| 3.3  | Behavior of parallel processes                  | 42 |

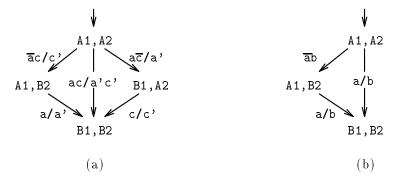

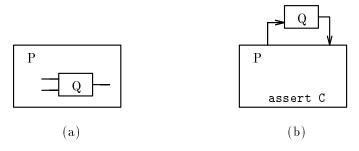

| 3.4  | Local signal definition                         | 43 |

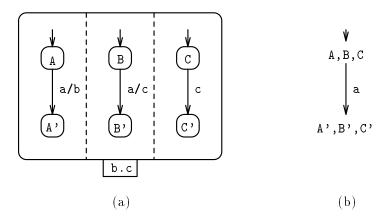

| 3.5  | Hierarchical decomposition                      | 45 |

| 3.6  | Absence of behavior                             | 46 |

| 3.7  | Implicit nondeterminism                         | 47 |

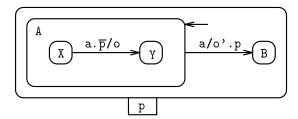

| 3.8  | Exception handling                              | 48 |

| 3.9  | Normal termination                              | 48 |

| 3.10 | Process interrupt                               | 49 |

| 3.11 | The control automaton of the stopwatch          | 50 |

| 3.12 | The running modes of the digital watch          | 52 |

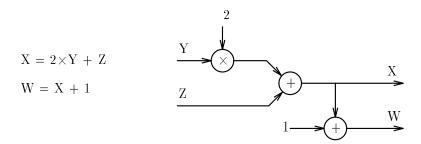

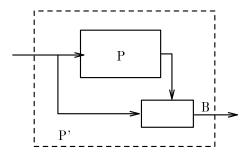

| 4.1  | Descriptions of a data-flow system              | 54 |

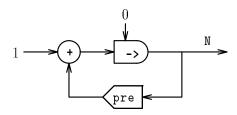

| 4.2  | Operator net of the counter                     | 60 |

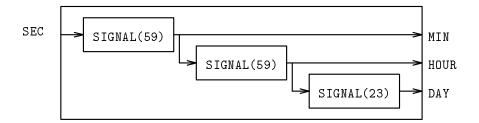

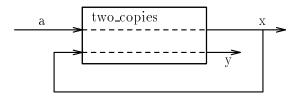

| 4.3  | Model instanciation in Signal                   | 72 |

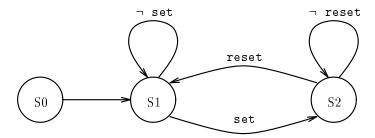

| 5.1  | Lack of behavior                                | 78 |

| 5.2  |                                                 | 79 |

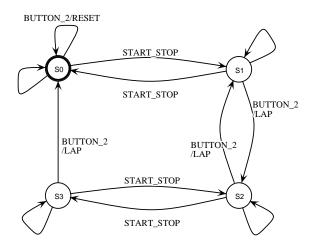

| 6.1  | The control automaton of the button interpreter | 90 |

| 6.2  | A looping call                                  | 93 |

| 6.3  |                                                 | 99 |

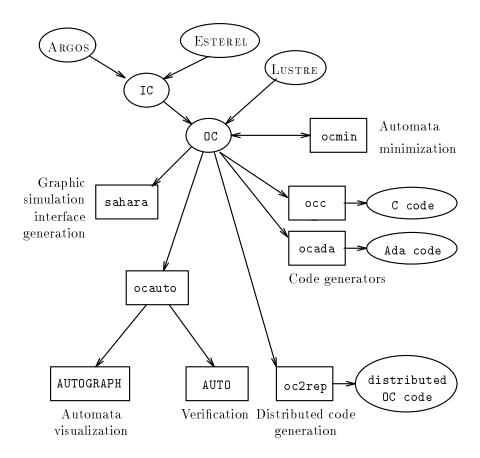

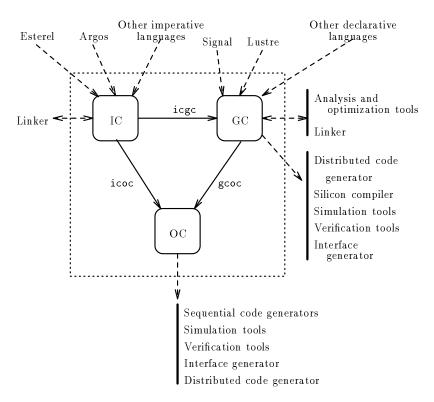

| 6.4  | The common environment Esterel/Lustre/Argos 1   | 01 |

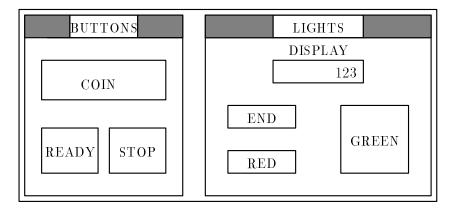

| 6.5  | The Sahara intrument panel of the reflex game 1 |    |

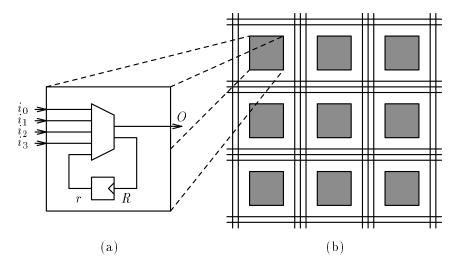

|   | 8.1                                                           | A simple programmable active memory                                                                                                                                                                                                                  |

|---|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

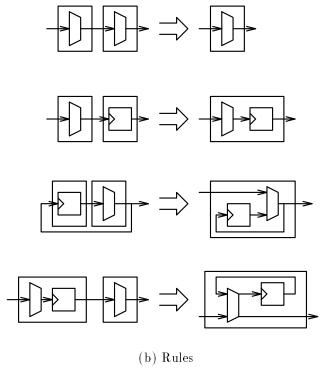

|   | 8.2                                                           | Some rules for packing operators into PABS                                                                                                                                                                                                           |

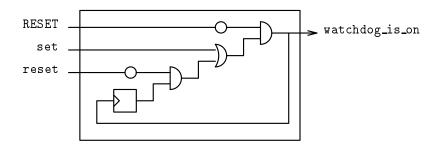

|   | 8.3                                                           | The cell computing the variable "watchdog_is_on" 123                                                                                                                                                                                                 |

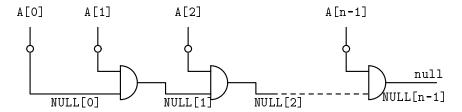

|   | 8.4                                                           | The net of the zero comparator                                                                                                                                                                                                                       |

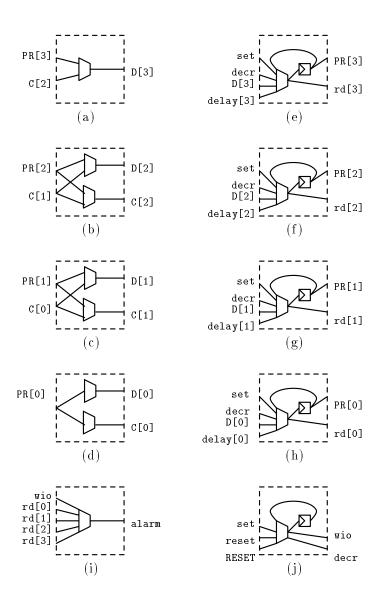

|   | 8.5                                                           | Layout of the watchdog on Perle-0                                                                                                                                                                                                                    |

|   | 8.6                                                           | First circuit                                                                                                                                                                                                                                        |

|   | 8.7                                                           | Second circuit                                                                                                                                                                                                                                       |

|   | 9.1                                                           | Verification program                                                                                                                                                                                                                                 |

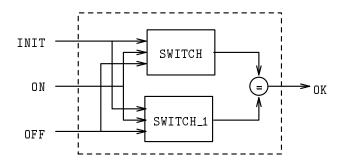

|   | 9.2                                                           | Assumption-dependent equivalence of programs 146                                                                                                                                                                                                     |

|   | 9.3                                                           | Modular verification                                                                                                                                                                                                                                 |

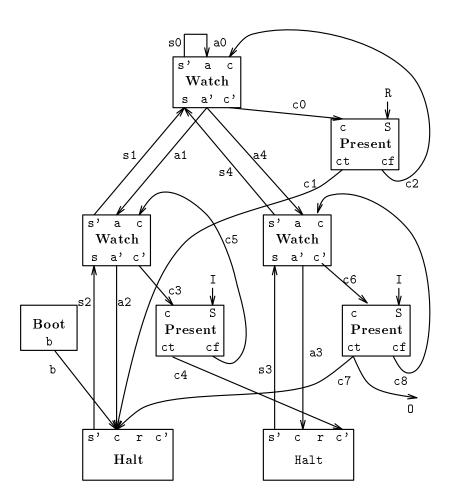

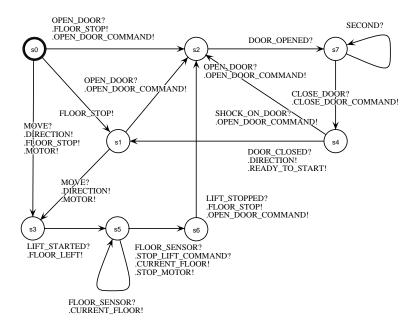

|   | 10.1                                                          | The full automaton of a lift controller                                                                                                                                                                                                              |

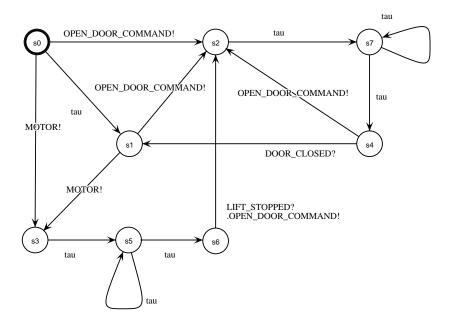

|   | 10.2                                                          | Simplified automaton                                                                                                                                                                                                                                 |

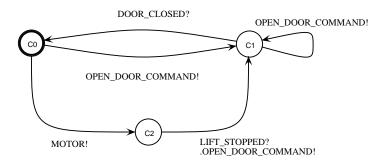

|   | 10.3                                                          | Reduced automaton                                                                                                                                                                                                                                    |

|   | 11.1                                                          | The common environment of synchronous languages 158                                                                                                                                                                                                  |

|   |                                                               |                                                                                                                                                                                                                                                      |

| _ | •                                                             | , em 11                                                                                                                                                                                                                                              |

| L | is                                                            | t of Tables                                                                                                                                                                                                                                          |

| L | 4.1                                                           | t of Tables  Boolean flows and clocks                                                                                                                                                                                                                |

| L |                                                               |                                                                                                                                                                                                                                                      |

| L | 4.1                                                           | Boolean flows and clocks                                                                                                                                                                                                                             |

| L | 4.1<br>4.2                                                    | Boolean flows and clocks                                                                                                                                                                                                                             |

| L | 4.1<br>4.2<br>4.3                                             | Boolean flows and clocks                                                                                                                                                                                                                             |

| L | 4.1<br>4.2<br>4.3<br>7.1                                      | Boolean flows and clocks                                                                                                                                                                                                                             |

| L | 4.1<br>4.2<br>4.3<br>7.1<br>7.2                               | Boolean flows and clocks                                                                                                                                                                                                                             |

| L | 4.1<br>4.2<br>4.3<br>7.1<br>7.2<br>7.3<br>7.4                 | Boolean flows and clocks                                                                                                                                                                                                                             |

| L | 4.1<br>4.2<br>4.3<br>7.1<br>7.2<br>7.3<br>7.4<br>10.1         | Boolean flows and clocks56Filtering and projection59Nodes and clocks61Code replication116Placement of emission statements113Placement of receiving statements113Example of distributed code113                                                       |

| L | 4.1<br>4.2<br>4.3<br>7.1<br>7.2<br>7.3<br>7.4<br>10.1<br>10.2 | Boolean flows and clocks56Filtering and projection59Nodes and clocks66Code replication110Placement of emission statements111Placement of receiving statements113Example of distributed code113Transition table of the $\tau$ -saturated automaton153 |

#### *Foreword*

This book will attempt to give a first synthesis of recent works concerning reactive system design. The term "reactive system" has been introduced in order to avoid the ambiguities often associated with by the term "real-time system," which, although best known and more suggestive, has been given so many different meanings that it is almost inevitably misunderstood. Industrial process control systems, transportation control and supervision systems, signal-processing systems, are examples of the systems we have in mind.

Although these systems are more and more computerized, it is surprising to notice that the problem of time in computer science has been studied only recently by "pure" computer scientists. Until the early 1980s, time problems were regarded as the concern of performance evaluation, or of some (unjustly scorned) "industrial computer engineering," or, at best, of operating systems.

A second surprising fact, in contrast, is the growth of research concerning timed systems during the last decade. The handling of time has suddenly become a fundamental goal for most models of concurrency. In particular, Robin Milner's pioneering works about synchronous process algebras gave rise to a school of thought adopting the following abstract point of view: As soon as one admits that a system can instantaneously react to events, i.e., if the execution time of the machine is considered negligible with respect to the response delays of its environment, the time behavior of a system can be formalized in a very simple and elegant way.

The third surprise is that this synchronous point of view was applied to programming almost exclusively by French projects. Three projects started, quite independently, in the early 1980s, aiming at designing the three synchronous programming languages ESTEREL (ENSMP & INRIA), SIGNAL (INRIA/IRISA), and LUSTRE (IMAG). Other languages like SML, STATECHARTS, or L.O, which were developed in other countries, adopt some aspects of the synchronous model; but on the one hand, these languages do not thoroughly use this model, and on the other hand, they were not designed to be used for programming (SML is a hardware description language, STATECHARTS were designed as a specification language.

guage, and L.O is a language for specifying communication protocols). The three French groups rapidly noticed that their languages were based on the same model. A tight cooperation was set up, that focused in particular on compiling methods and broadcasting the synchronous point of view to the industrial world. This community was joined by another, more recent project, concerning the language Argos (IMAG), a purely synchronous variant of Statecharts.

This book is therefore a survey of very recent work, some of which is still under development. Being myself strongly involved in the development of one of these languages — the language Lustre — I cannot claim to give a fully unbiased presentation: it is often influenced by my personal opinion and my present knowledge of the subjects. On the other hand, several parts of this book have been partially borrowed from existing papers devoted to each language. For their permission to borrow this material, and for many helpful comments about the manuscript, I would like to thank Gérard Berry, Albert Benveniste, Paul Caspi, Paul Le Guernic, and Florence Maraninchi. I am also grateful to Corinne Pichon, who carefully corrected the English version.

A first draft of this book (written in French) was used as lecture notes for a 12-hour course given at the 21th AFCET International School of Computer Science, held in San Sebastian (Spain) in July 1991.

# List of academic and industrial contacts concerning each language

## Esterel:

- Gérard Berry, CMA/ENSMP, Sophia Antipolis 06565 Valbonne, France

- Jean-Pierre Paris, CISI-Ingéniérie, Sophia Antipolis 06565 Valbonne, France

- Philippe Couronné, ILOG S.A., 2, Avenue Galiéni -94253 Gentilly, France

## Argos:

• Florence Maraninchi, IMAG, B.P. 53 - 38041 Grenoble, France

## Lustre:

- Paul Caspi or Nicolas Halbwachs, IMAG, B.P. 53 38041 Grenoble, France

- Daniel Pilaud, VERILOG, ZAC du Pré Millet 38330 Montbonnot, France

## Signal:

- Albert Benveniste or Paul Le Guernic, IRISA/INRIA, Campus de Beaulieu - 35042 Rennes, France

- François Dupont, TNI, ZI du Vernis 29608 Brest, France

## Explanation of acronyms

ENSMP: Ecole Nationale Supérieure des Mines de Paris

INRIA: Institut National de Recherche en Informatique et Automatique

IRISA: Institut de Recherche en Informatique et Systèmes Aléatoires

IMAG: Institut d'Informatique et de Mathématiques Appliquées de Grenoble

## Chapter 1

## Introduction

## 1.1 Reactive systems

Reactive systems are computer systems that continuously react to their environment at a speed determined by this environment. This class of systems has been introduced [HP85, Ber89] in order to distinguish these systems, on the one hand, from transformational systems — i.e., classical systems, whose inputs are available at the beginning of the execution and which deliver their outputs when terminating — and, on the other hand, from interactive systems, which continuously interact with their environment, but at their own rate (e.g., operating systems). Most industrial "real-time" systems are reactive — control, supervision and signal-processing systems — but other examples concern communication protocols or man-machine interfaces.

The main features of these systems are the following:

They involve concurrency: At the least, the concurrency between the system and its environment must be taken into account. Moreover, it is often convenient and natural to consider such a system as made of a set of parallel components, that cooperate to achieve the intended behavior. Finally, these systems are sometimes implemented on parallel or distributed architectures in order to increase their performances or their reliability. However, let us note that the logical decomposition of a system into parallel processes generally has nothing to do with an actual concurrent implementation, and, even if such a concurrent implementation is performed, the physical decomposition is not necessarily the same as the logical one. There is no reason for a logical decomposition of a problem into subproblems to satisfactorily meet performance or fault tolerance criteria on a given architecture.

They are submitted to strict time requirements: These requirements concern both their input rate and their input/output response time. These constraints must be expressed in the system specifications, they must be taken into account during the system design, and their satisfaction must be checked on the implementation. Time-constraint fulfillment obviously requires efficient implementation, but it especially necessitates precise evaluation of execution time.

They are generally deterministic: The outputs of such a system are entirely determined by their input values and by the occurrence times of these inputs. This determinism distinguishes reactive systems from interactive ones: most interactive systems are intrinsically nondeterminist. An operating system contains, for instance, schedulers that dynamically activate and interrupt processes according to various parameters (CPU load, resource availability, priorities, ...). The result of a call to the system generally depends on these parameters. The design, analysis, and debugging of a deterministic system are much easier. So the inherent determinism of reactive-system specifications must be preserved in their implementation.

Their reliability is an especially important goal: This may be their most important feature. It is a commonplace to say that errors in reactive systems can have dramatic consequences, involving human lives and huge amount of money. The economic and human consequences of an error in the software driving a satellite or controlling a nuclear plant can obviously be incalculable. Therefore, these systems require especially rigorous design methods and constitute a field where formal verification must be considered.

Generally, they are made partly by software and partly by hardware: Many reactive systems are still implemented by hardware, for reasons of cost or performance or for historical reasons. In many

other cases, they are partly implemented by hardware, and the hardware and software parts are separated quite late during the design.

## 1.2 Classical approaches

As noted above, reactive systems have been for a long time (and often still are) implemented by hardware (analog machines, switch systems, and custom circuits). When implemented by software, they are often programmed in assembly language for efficiency purposes. At a higher level, "operating system" approaches (real-time monitors) or general-purpose parallel languages are used. Models include automata or Petrinet-based models, task-based models, and communicating processes.

Deterministic automata: Automata are often used to implement the control kernel of a reactive system. Given a set of input values, the automaton selects a transition from its current state, calls the corresponding sequential tasks, and changes its state for its next reaction. Such an approach generally leads to excellent and measurable performances; a reaction is a "linear" piece of code (neither loop nor recursivity, no interrupt, no overhead due to process management), whose maximal execution time can be accurately bounded. Moreover, automata are well-known mathematical objects for which verification techniques are available (evaluation of temporal logic formulas [CES86, QS82], reduction and observation [Ver86, Fer90]).

However, automata are "flat" objects, without any hierarchical or parallel structure. Consequently, they are very difficult to use to design complex systems. Writing an automaton with about ten states only is a difficult and error-prone task. The slightest modification in the system specifications may involve a complete modification and rewriting of the automaton.

**Petri-net-based models:** These models are mainly used to program industrial controllers. The inherent concurrency of these models reduces the complexity of system description. However, because of the lack of hierarchy, they are hard to apply to big systems. Moreover, their semantics, especially concerning time aspects, is often unclear.

Task-based models: Here, we mean the approach consisting in designing a system as made of a set of sequential tasks, activated and controlled by a real-time operating system. The system is decomposed into tasks that generally communicate with each other by means of a shared memory. In our opinion, this is a low-level approach. Time constraints are not directly expressed in the description; they can only be satisfied by means of scheduling instructions (interrupts, priorities, ...) given to the operating system. Program portability is doubtful. System analysis is made difficult because of nondeterminism and lack of a global view. Performances can deteriorate because of tasks management and dynamic scheduling.

Communicating processes: General-purpose parallel languages, such as ADA [ADA83] or OCCAM [INM84] are on a higher level. These languages offer high-level primitives to structure programs and data. Communication and synchronization mechanisms (rendezvous, fifo queues, . . .) are much cleaner than shared memory. These languages have been designed in order to increase program portability. However, this portability is achieved at the expense of nondeterminism. For a program behavior to be independent of the target architecture (monoor multiprocessor), only minimal assumptions are made about interprocess synchronization. Even if some of these languages have been provided with "real-time" primitives, the semantics of these primitives is generally vague. We illustrate these problems by means of a classical example of an ADA program, where a task A signals "minutes" to a task B, by counting "seconds":

```

loop

delay 60; B.MINUTE

end

```

This program does not provide the intended behavior: for a MINUTE to be received by B, A must have been waiting for 60 seconds, but B must also listen to it, and, moreover, the rendezvous must take place — and the occurrence time of this rendezvous is left unspecified in the language semantics. The delay separating two successive receptions of MINUTE is at least 60 seconds. On the other hand, a signal cannot be broadcast: if A must send MINUTE to a third task C, A must also execute C.MINUTE. B

and C will never receive MINUTE at the same time. In such a language, different processes never have the same view of the global state of the program. The last drawback of general-purpose parallel languages for real-time programming is the tremendous overhead that can be involved by runtime process management.

As a conclusion to this brief overview of classical tools to reactive system design, let us notice that the user must choose between determinism and concurrency. All parallel languages are based on asynchronous execution schemes, where processes compete with each other for resources, and where this competition is nondeterministically solved. Synchronous languages may be viewed as an attempt to reconcile concurrency and determinism.

## 1.3 The synchronous approach

Synchronous languages have been designed to make the programmer's task easier, by providing him with "ideal" primitives, which allow a program to be considered as *instantaneously* reacting to external events. Each internal or output event of the program is precisely dated with respect to the flow of input events. The behavior of a program is fully deterministic, both from the functional and from the time point of view.

In fact, the notion of physical (chronometric) time is replaced by a simple notion of order among events: the only relevant notions are the simultaneity and precedence between events. Physical time does not play any special role (as it does in ADA); it will be handled as an external event, exactly as any other event coming from the program environment. This is called the *multiform notion of time*. As an example, let us consider the two following requirements:

and "The train must stop within 10 seconds"

"The train must stop within 100 meters"

Conceptually, these two constraints are of the same nature. However, in a language where physical time (counted in "seconds") plays a particular role and is handled by special statements, they will be expressed in completely different ways. In the synchronous model, they will be expressed by similar precedence constraints:

"The event *stop* must precede the 10th (respectively, 100th) next occurrence of the event *second* (respectively, *meter*)"

When we will speak of an instant, this notion will be understood as a logical instant: the history of a system is a totally ordered sequence of logical instants; at each of these instants, zero, one, or several events occur. Event occurrences that happen at the same logical instant are considered simultaneous; those that happen at different instants are ordered as their instants of occurrence. Apart from these logical instants, nothing happens either in the system or in its environment. Finally, all the processes of the system have the same knowledge of the events occurring at a given instant.

In practice, the synchrony hypothesis is the assumption that the program reacts rapidly enough to perceive all the external events in suitable order. If this assumption is satisfied — and, more importantly, if its satisfaction can be checked — the synchronous hypothesis is rather a more realistic abstraction than the one that consists in considering that a machine deals with "actual" integer or real numbers. Moreover, we will see that synchronous languages can be implemented in a particularly efficient and measurable way. The object code is structured as a finite automaton, a transition of which corresponds to a reaction of the program. As noted before, the code corresponding to such a transition is linear (loop-free), and its maximal execution time can be accurately bounded on a given machine. Therefore, the validity of the synchrony hypothesis can be checked.

## 1.4 Complex systems

However, synchronous languages do not pretend to solve all the problems raised by the design of real-time systems. A real-life complex system generally involves the cooperation of the three types of programs: for instance, a programmer makes use of a reactive interface (keyboard, mouse, scrollbar) to call interactive services of the operating system and to activate transformational tasks. Generally speaking, following [BG92], we can distinguish three parts in a complex real-time system:

- A generally interactive *interface* with the environment, which acquires the inputs and processes the outputs. This level includes interrupt management, input reading from sensors, and conversion between logical and physical inputs/outputs. This level can also deal with the communication between several loosely coupled, synchronous components.

- One or more reactive kernels. Such a kernel computes the outputs from the logical inputs, by selecting the suitable reaction (computations and output emissions) to incoming inputs.

- A level of *data management*, which performs transformational tasks under the control of the reactive kernel.

This book essentially deals with reactive kernel design, which is the most specific and probably the most difficult part of the design of a complex real-time system. One must keep in mind, however, that these kernels are intended to be merged into more complex systems. As a consequence, synchronous languages are not complete languages. In particular, they do not offer primitives to define and handle complex data structures, which are left to a classical language (host language). Moreover, synchronous language compilers produce their object code in the host language, for this code will later on be integrated into a larger program.

## 1.5 Summary of this book

We will present the work concerning four languages: ESTEREL, ARGOS, LUSTRE, and SIGNAL. Rather than describing successively the parts concerning each of them, we prefer to sort them according to some general topics:

- Part I of this book presents each language, together with illustrating examples of programs. Examples have been chosen in order to highlight the most specific features of each language.

- Part II deals with compilation. We will successively present:

- nonclassical static verifications performed by compilers: causality checking in ESTEREL (§5.1) and ARGOS (§5.2), clock checking in LUSTRE, (§5.3) and clock synthesis in SIGNAL (§5.4).

- sequential code generation from ESTEREL (§6.1) and LUSTRE (§6.2) programs. ESTEREL and LUSTRE compilers share an original method to synthesize the control structure of the object code as a finite automaton. Both compilers generate the code in a common format, called oc (for "object code"), on which several tools can be applied (§6.3).

- distributed code generation. Two very different approaches will be presented. The first one has been applied to Signal and makes use of the logical concurrency expressed in the source program. The second approach has been developed for Lustre, but can be applied to any language compiled towards oc, since it requires first the generation of sequential code.

- silicon compiling, from ESTEREL and LUSTRE (Chapter 8).

- Part III is devoted to program verification. The language LUSTRE itself can be used to express properties about programs (Chapter 9); these properties are checked by an exhaustive analysis of the automaton built by the compiler. Another approach, used to verify ESTEREL programs (Chapter 10), consists of reducing the generated automaton according to various suitable observation criteria.

# Part I Four Synchronous Languages

## Chapter 2

## The imperative language Esterel

## 2.1 Introduction

Among the languages we will present, ESTEREL is the oldest, since its design started in the early 1980s. It was developed in Gérard Berry's group and is a common project of INRIA and ENSMP in Sophia-Antipolis.

ESTEREL is an imperative, textual language, and its syntax is close to usual parallel languages. Paradoxically, because of this apparent analogy with classical languages, ESTEREL will be the best language to highlight the specificity of the synchronous approach. The formalization of fundamental concepts of synchronous programming is mainly a consequence of the design of ESTEREL, and the method to compile synchronous programs into automata was first proposed in the ESTEREL compiler. Today, ESTEREL is a commercial product (sold and maintained by two French software companies: CISI-Ingenierie and Ilog) that is actually used in the industry. The following overview of the language is essentially derived from [BCG87, BCG88].

## 2.2 Basic concepts

An Esterel program communicates with its environment by means of signals and sensors. Signals are used both as inputs and outputs,

while sensors are used only as inputs. Signals can convey values; sensors always do. For instance, a train controller can receive a signal every millisecond, a signal every wheel revolution, track signals conveying positional informations, and signals coming from the operator keyboard; it can use sensors to measure the external temperature; it can emit power commands to the engines and brakes. It can be made of submodules, communicating with each other by means of internal signals.

Signals and sensors are identified by names. The notation S(v) expresses that the signal S conveys the value v.

Signals are broadcast among all the processes (though this broadcasting may be limited by scope rules; see below). When a signal is emitted (either by the environment or by an internal process), it is instantaneously perceived by all the processes that listen to it. One can think of programs as communicating via radio waves, each signal being represented by a frequency. Two kinds of information are broadcast on the waves: values, which are permanent, and signal tops, which are transient (they cannot be perceived by processes that do not listen to the signal when it occurs). A sensor has a value but no signal top. A pure signal has a signal top but no value. A valued signal has both, and a value change is always synchronous with a signal top (hence, the signal top is used to broadcast and detect value changes; there is no way to detect sensor value changes).

Values conveyed by signals can appear in expressions: if S is the name of a valued signal or of a sensor, ?S denotes its current value. A signal top is a control information that is handled by special control statements.

In ESTEREL, control takes no time. The occurrence of an input signal can instantaneously result in the emission of other signals. As a consequence, the following program fragment

```

every 60 SECOND do

emit MINUTE

end

```

precisely emits the signal MINUTE every 60 occurrences of the signal SECOND. The emission of MINUTE is simultaneous with the 60th occurrence of SECOND.

This notion of simultaneity is captured by the concept of *event*. An event is a set of simultaneous occurrences of (possibly valued) signals. A particular run of a program is a sequence of events, called a *history*. We give below a possible history of a speed counter, receiving two signals SECOND and METER, and computing the valued signal SPEED every second:

```

{\tt \{METER\}}, {\tt \{SECOND, SPEED(1)\}}, {\tt \{METER\}}, {\tt \{METER, SECOND, SPEED(2)\}}, ...

```

There is a special built-in pure signal named tick that implicitly belongs to any event. In other words, tick occurs at any reaction of the program.

The same signal may be emitted several times at the same instant (e.g., by several processes). If such a signal is pure, the result is only that the signal is present in the current event. If it is a valued signal, it can be associated a "combination operator," noted by \*: the result of the simultaneous emission of  $S(v_1),S(v_2),\ldots,S(v_n)$  is then the occurrence of  $S(v_1*v_2*\cdots*v_n)$  in the current event. As an example of the use of this combination mechanism, in ETHERNET-like local networks, signal broadcasting is physically realized on a cable. A special value NAK represents the collision of two messages. One sets  $v_1*v_2=NAK$  for all  $v_1,v_2$ .

## 2.3 Programming primitives

The basic programming unit is the module, which contains a declaration part and a statement part.

Like all the synchronous languages considered here, ESTEREL is not a complete language. Data types, constants, functions, and procedures can be imported from a host language and are only declared as abstract names in the declaration part. Only a minimal set of types, constants, and operators are built in (integers, Boolean, usual arithmetic and logic operators).

#### 2.3.1 Declarations

In the declaration part, we declare the types, constants, functions, and procedures used by the module (and defined in the host language); we then declare the signals and the sensors that define the module's interface. Finally, the declaration part may also include "relations," which are implication and exclusion relations among input signals; these are known properties of the environment, which are indicated to the compiler for optimization purposes. Here is a possible declaration part of a TIMER module, as it appears in the digital watch program described in [Ber91b]:

The procedure INCREMENT\_TIME is declared with two lists of types: the first list types arguments passed by reference, and the second list types arguments passed by value (it is empty here). The output signal TIMER\_VALUE conveys a value of type TIME and has no combination operator: its multiple emission is forbidden (it will be checked by the compiler). The multiple emission of the output signal BEEP is allowed: the integer values conveyed will then be added. Intuitively, several components of a watch can operate the beeper: the chime beeps once a second, the stopwatch beeps twice a second, and the alarm beeps four times a second. If some of these components beep together, the beep frequencies must be added. Finally, the given relation indicates that signals SECOND and RESET never occur at the same time (the # operator denotes exclusivity).

## 2.3.2 Expressions

The expressions are classically built from variables, constants, signal and sensor values (?S), and function calls.

#### 2.3.3 Statements

There are two kinds of statements: primitive statements and derived statements, which are defined in terms of primitive statements. The primitive statements are themselves divided into two groups: classical basic imperative statements, and temporal statements that deal with signals.

## Basic imperative statements

Here is the list of the basic imperative statements:

| nothing                                                                  | dummy statement            |

|--------------------------------------------------------------------------|----------------------------|

| halt                                                                     | halting statement          |

| <pre><var> := <expression></expression></var></pre>                      | assignment                 |

| <pre>call <id> (<var_list>)(<exp_list>)</exp_list></var_list></id></pre> | external procedure call    |

| <stat>;<stat></stat></stat>                                              | sequence                   |

| if <exp> then <stat></stat></exp>                                        |                            |

| else <stat> end</stat>                                                   | conditional                |

| loop <stat> end</stat>                                                   | infinite loop              |

| <stat>    <stat></stat></stat>                                           | parallel statement         |

| trap <id> in <stat></stat></id>                                          | trap definition            |

| exit <id></id>                                                           | exit from trap             |

| var <var_decls> in <stat> end</stat></var_decls>                         | local variable declaration |

| signal <signal_decls></signal_decls>                                     |                            |

| in <stat> end</stat>                                                     | local signal declaration   |

| run <name> <renaming></renaming></name>                                  | module instanciation       |

There are no shared variables: if a variable is updated in one branch of a parallel statement, it cannot be read or written in the other branches.

Remember that the execution machine is *infinitely fast*. The only statement that takes time is the halt statement, which does nothing and never terminates.<sup>1</sup> Therefore, nothing does nothing in no time, assignment and external procedure calls are instantaneous, the second statement of a sequence is started exactly when the first statement ter-

$<sup>^{1}\</sup>mathrm{We}$  will see later that the infinite execution of a halt statement can be interrupted.

minates, and the branches of a parallel statement start simultaneously; a parallel statement terminates synchronously with the last termination of its branches. Hence, when a parallel statement is started, its branches work in the same signal environment.

The trap\_exit mechanism is a classical escape mechanism: a trap defines a block that is instantly exited when a corresponding exit statement is executed. If several nested blocks are simultaneously exited, the effect is to instantly exit the outermost one. This mechanism is perhaps the most powerful control mechanism in ESTEREL. It extends to general exception facility.

The run statement allows module reuse. Its effect is a copy in place of the code of the module whose name is given. Some input/output signals can be renamed (by default, they are not). We will see later some examples of use of this statement.

Although statements are simultaneously executed, they are executed in the right order. Hence, a sequence

$$X := 0 : X := X+1$$

instantly yields X=1. Only finitely many statements can be executed simultaneously. One imposes a statically checked finiteness constraint to forbid loops like

$$X := 0$$

; loop  $X := X+1$  end

#### Temporal statements and signal handling

All statements described so far "take no time," except halt. We now describe temporal statements that handle signals and can take time.

The signals can be either emitted by the program's environment or by the program itself. To emit a signal S conveying the value of an expression <exp>, one writes

or simply "emit S" if S is a pure signal. An emission is instantaneous. If several emissions occur simultaneously, the values are combined, as described on page 13.

For signal reception, there are two primitive statements. The first tests for the presence of a signal in the current event:

present S then <statement1> else <statement2> end

or, for a valued signal,

present S(X) then <statement1> else <statement2> end

The semantics is clear: if S is present in the current event, then <statement1> is instantly started. Otherwise, <statement2> is instantly started. In the case of a valued signal, if the signal is present, the variable X instantly takes the value conveyed by the signal.

The second statement is the most important ESTEREL construct. It is called the *watchdog* and has the form

do

<statement>

watching <occ>

where <statement> is any statement and where <occ> is an occurrence of a signal. An occurrence is either a signal name (e.g., SECOND) possibly preceded by the keyword immediate, or a signal name preceded by a count factor (e.g., 3 SECOND). This statement defines a time limit for the execution of its body. The time limit is defined by the occurrence <occ>. If <occ> has the form S (respectively, immediate S), the time limit is the first event in the strict future of the current event (respectively, in the future, including the current event) that contains an occurrence of the signal S. Similarly, for an occurrence n S, the time limit is the nth event in the strict future to contain S.

The body <statement> is started simultaneously with the watching statement (except if <occ> has the form immediate S and if S is present). It is executed up to the time limit excluded:

- If the body terminates strictly before the limit, the whole watching statement terminates synchronously;

- If the body is not terminated when the limit occurs, the body is instantly killed without being executed at that time and the watching statement terminates.

Notice that the nesting of watching statements establishes a natural preemption priority. Consider the following example:

```

do

do

<statement1>

watching S1;

<statement2>

watching S2

```

If S1 and S2 occur simultaneously, then the outermost watching statement is terminated, and <statement2> is not executed. Hence S2 preempts a simultaneous S1.

Let us also notice that we have now two basic ways to kill a statement <stat> on the occurrence of a signal S:

```

- the interrupt do <stat> watching S, and

```

- the withdrawal<sup>2</sup>

The difference is that in the first case, when S occurs, the statement <stat> is not executed at that time (the interruption precedes the reaction), whereas in the second case, <stat> reacts before being killed (it can express its last wishes!).

#### **Derived statements**

Many useful temporal statements can be derived from primitive ones. For instance, one writes

```

await <occ> instead of halt watching <occ>

```

<sup>&</sup>lt;sup>2</sup>see the definition of the await statement in the next section

```

do do stat> instead of stat>; halt upto <occ> watching <occ>

```

The await statement has its intuitive meaning: it does nothing and terminates as soon as the awaited occurrence <code><occ></code> happens. Notice that many "real-time" languages offer such a statement (often with less precise semantics) as a primitive. However, though await can be derived from the watching statement, the converse is not true. So, the watching statement is more primitive and powerful. The difference between the upto and the watching statements is that "do <code><stat></code> upto <code><occ></code>" does not terminate when its body does, but always waits for <code><occ></code>. The watching statement could have been derived from the upto by writing

It is often useful to add a *timeout* clause to a watchdog; this clause is executed if the time limit occurs before termination of the body. We will then write

If <stat1> terminates strictly before <occ>, the block "trap" is instantly exited, and the timeout clause <stat2> is ignored.

```

and

every 5 SECOND do

<stat>

end

instead of

end

await 5 SECOND;

loop

<stat>

each 5 SECOND

```

In a "loop ...each <occ>" statement, the body starts immediately and is restarted on every occurrence of <occ>; an "every <occ> do ..." first waits for the first occurrence of <occ>.

Multiple waiting of signals is written

```

await

case <occ1> do <stat1>

case <occ2> do <stat2>

...

case <occn> do <statn>

end

```

Unlike similar statements in asynchronous languages, this selection is deterministic: the first occurrence determines the statement to be executed. If several occurrences simultaneously happen, the statement corresponding to the first such occurrence in the list is selected (therefore, the order in the list establishes a priority relation between simultaneous occurrences). The expansion of the multiple waiting is of the form

```

do

do

do

do

do

halt

watching <occn>

timeout <statn> end

watching <occ2>

timeout <stat2> end

watching <occ1>

timeout <stat1> end

```

A last useful derived statement allows the emission of a signal at each program reaction. It makes use of the predefined "always present signal" tick (cf. page 13). One can write

sustain S instead of emit S each tick

## 2.4 Programming style and first examples

Before giving some examples, we illustrate some specific aspects of ESTEREL programming: the use of several time scales, the use of signal broadcasting, and simultaneity.

## 2.4.1 Using signals as time units

The multiform-time point of view, generally adopted in synchronous programming, has been described before. In ESTEREL, this point of view consists in using any signal as a "time unit" to count "delays." An illustrating example appears in the "reflex game," which will be treated later (§2.6). The core of the system must satisfy the following specification:

Wait for a hit on a READY button within a time limit of 10 SECOND; in case of timeout, emit an ALARM; while waiting, any hit on the STOP button should ring a BELL.

The corresponding program could be

do

do

every STOP do emit RING\_BELL end

upto READY

watching 10 SECOND

timeout emit ALARM end

(Here "upto READY" is equivalent to "watching READY;" we prefer using upto whenever we are not interested in the termination of the body)

Let us now consider the following specification:

Wait for 10 SECOND; if STOP is hit during that time, terminate and emit an ALARM; while waiting, any hit on READY should ring the BELL.

This leads to the following program:

```

do

do

every READY do emit RING_BELL end

upto 10 SECOND

watching STOP

timeout emit ALARM end

```

In some sense, this program appears to be *dual* to the first one; it can be read as

```

Wait for 10 SECOND within a time limit of STOP; in case of timeout, emit an ALARM; while waiting ...

```

This symmetry comes from the fact that all signals play a similar role. The symmetry would completely disappear in a language like ADA, where the "real-time" (counted in seconds) plays a particular role and is handled by specific statements.

## 2.4.2 Use of broadcasting

Broadcasting simplifies process communication and improves modularity; when a process emits a signal, it does not need to know who is listening to that signal; conversely, when a process receives a signal, it does not need to know the emitter(s).

We illustrate this with the wristwatch example described in detail in [Ber91b]. A wristwatch is an excellent example of a reactive system; it is relatively small, but surprisingly complex, and has many features encountered in other systems: folding numerous commands into few buttons by using command modes, showing numerous data in few displays using display modes, and establishing communications and instantaneous dialogues between submodules. The wristwatch has five submodules: a WATCH that acts as a regular timekeeper, a STOPWATCH, an ALARM, a BUTTON\_INTERPRETER that interprets wristwatch buttons as commands directed to the other modules according to the current command mode, and a DISPLAY\_HANDLER that handles the various displays. Broadcasting makes life easier in several places:

- The external signal SECOND is automatically broadcast to all the modules that need it.

- Hitting a particular button in a particular mode provokes the toggling from 24H to AM/PM time display mode. This change concerns the watch and the alarm. The button interpreter broadcasts a message TOGGLE\_24H\_MODE\_COMMAND without worrying about who is expecting this message. Adding a second alarm would not modify the corresponding code.

- The timekeeper broadcasts a WATCH\_TIME signal whenever its internal time changes. This signal is used by both the alarm and the display handler. Adding a second alarm can be done without any modification of the WATCH and ALARM modules.

## 2.4.3 Instantaneous dialogue

The synchrony hypothesis allows a new form of communication, the instantaneous dialogue. A typical example appears in the wristwatch code, more precisely in the body of the stopwatch; it will be abstracted here. An instantaneous dialogue can be used whenever the behavior of a process P depends on some property of the internal state of another process Q. For simplification, assume that Q is a flip-flop on some signal FLIP\_FLOP\_COMMAND and that P must perform  ${\text{stat1}}$  if Q is in the "flip" state and  ${\text{stat2}}$  otherwise. Then we introduce two signals ARE\_YOU\_FLIP and I\_AM\_FLIP and writes Q as follows:

```

loop

do

loop

emit I_AM_FLIP

each ARE_YOU_FLIP

||

<flip state code>

upto FLIP_FLOP_COMMAND;

do

<flop state code>

upto FLIP_FLOP_COMMAND

end

```

Now, the intended behavior of P is ensured by the following code:

This example has been given to show the power of the assumption of simultaneity. However, instantaneous dialogues can often be avoided by using the sustain statement (tick and sustain were introduced late in the design of ESTEREL). A simpler solution of the above example could be

Another way to avoid instantaneous dialogue is to use Boolean-valued signals: whenever Q enters its "flip" state, it emits FLIP(true); whenever it enters the "flop" state, it emits FLIP(false). Then P only has to check ?FLIP to know the state of Q:

All these solutions behave in exactly the same way, although the code generated for the last one may be slightly less efficient, since a part of the program control is hidden in a Boolean value (see §6.1).

#### 2.4.4 A stopwatch

Let us write an ESTEREL program implementing the stopwatch of the digital watch presented in [Ber91b]. We will successively consider several versions, highlighting the language modularity: each version will be built from the previous version.

#### Simple stopwatch

The basic stopwatch receives an input signal START\_STOP that alternatively puts it in "running" and "stopped" states. Initially the stopwatch is stopped. It also receives a signal HS each 1/100 second. The stopwatch computes an integer TIME, whose value is the total amount of time (counted in 1/100 second) spent in the "running" state. The program is the following:

```

module BASIC_STOPWATCH :

input START_STOP, HS;

output TIME (integer);

var TIME:=0 : integer in

loop % stopped state

emit TIME(TIME);

await START_STOP;

do % running state

every HS do

TIME := TIME+1;

emit TIME(TIME);

end

upto START_STOP

end

end.

```

This program computes a local variable TIME, initialized to 0, which will contain the value always conveyed by the signal TIME. This signal is emitted whenever the stopwatch becomes "stopped" (therefore it is emitted at the initialization, so as to give a value to ?TIME). It is also

emitted, with incremented value, whenever a 1/100 second occurs in the "running" state. The alternation between the "stopped" and "running" states is realized in a fashion similar to the "flip-flop" program (§2.4.3).

#### Stopwatch with "reset"

The second version of the stopwatch receives another input signal RESET, whose occurrence puts the stopwatch back in its initial state. ESTEREL allows a modular solution of this problem: whenever RESET occurs, a new basic stopwatch is instanciated. Intuitively, this is like throwing away the old stopwatch and taking a new one!

```

module STOPWATCH_1 :

input START_STOP, HS, RESET;

output TIME (integer);

loop

run BASIC_STOPWATCH

each RESET.

```

#### Intermediate time handling

Let us again complexify our example. A new input signal LAP now allows us to record an intermediate time (for instance, the time spent by a runner for one track lap) while continuing to measure the global time. One occurrence of LAP freezes the time on display, while the internal stopwatch time continues to be computed as before. The next occurrence of LAP puts the stopwatch back in a state displaying the running time. Once again, this new version is built from the previous one by putting it in parallel with a "lap-filter." The role of the lap-filter is to manage the display state ("time frozen" or "time running") and to prevent the output of the signal TIME in the "frozen" state. The following program runs in parallel the previous stopwatch — with the signal TIME renamed as INTERNAL\_TIME — and the lap-filter, which is again similar to the "flip-flop." Initially, and whenever RESET occurs, it enters the "running time" state, where it transmits any occurrence of the INTERNAL\_TIME to the environment. The LAP signal alternatively commutes between this state and the "frozen time" state, where the INTERNAL\_TIME is no longer transmitted.

```

module STOPWATCH_2 :

input START_STOP, HS, RESET, LAP;

output TIME (integer);

signal INTERNAL_TIME (integer) in

run STOPWATCH_1 [signal INTERNAL_TIME / TIME]

|| % lap-filter

loop

do

do % running time

every INTERNAL_TIME do

emit TIME(?INTERNAL_TIME)

end

upto LAP;

% frozen time

emit TIME(?INTERNAL_TIME);

await LAP

watching RESET

end % loop

end.

```

#### General stopwatch

An actual stopwatch has only two buttons:

- the first one corresponds to the START\_STOP signal.

- the interpretation of the second one depends on the global state of the stopwatch. When the stopwatch is stopped and the displayed time is running, it is interpreted as a RESET command; otherwise it corresponds to a LAP signal.

Such a folding of logical inputs onto a small number of physical inputs is very common in reactive systems. In order to preserve the modularity of our program, this folding will be entrusted to a "button interpreter," which computes the global state of the stopwatch. The corresponding module is the parallel composition of two flip-flops, computing the "running/stopped" state and the "running-time/frozen-time" state, with a process interpreting the signal BUTTON\_2 according to these states.

```

module BUTTON_INTERPRETER :

input START_STOP, BUTTON_2;

output RESET, LAP;

signal STOPWATCH_RUNNING, FROZEN_TIME in

every BUTTON_2 do

present STOPWATCH_RUNNING then emit LAP

else % the stopwatch is stopped

present FROZEN_TIME then emit LAP

else emit RESET

end

end

end

|| % flip-flop "running/stopped"

loop % stopped state

await START_STOP;

do % running state

sustain STOPWATCH_RUNNING

upto START_STOP

end

|| % flip-flop "running-time/frozen-time"

loop % running-time state

await LAP;

do % frozen-time state

sustain FROZEN_TIME

upto LAP

end

end.

The whole stopwatch program is the following:

module FULL_STOPWATCH:

input START_STOP, HS, BUTTON_2;

output TIME (integer);

relation START_STOP # HS # BUTTON_2;

signal RESET, LAP in

run CHRONO_2

run BUTTON_INTERPRETER

end.

```

However, this program is refused by the ESTEREL compiler, which emits the following error message:

```

user error: causality error:

Signals: RESET LAP FROZEN_TIME

```

This signals that our program contains a "causality loop." This type of error is specific to synchronous programs and will be analyzed in the following section.

## 2.5 Causality problems in Esterel

The synchronous hypothesis may cause temporal paradoxes, similar to short-circuits or oscillations in electronics or to deadlocks in parallel programming. We show here two kinds of such paradoxes, illustrated by short examples.

#### 2.5.1 Lack of behavior

Let us consider the following program:

```

signal S in

present S then

nothing

else

emit S

end

```

The local signal S must be emitted if and only if it is absent, which is clearly nonsense. This program behaves more or less like a "not" gate with output plugged on input. This kind of phenomenon caused the error in our stopwatch: in the button interpreter, the process interpreting the signal BUTTON\_2 decides to emit the LAP signal according to the presence of the signal FROZEN\_TIME. Assume that the flip-flop in charge of this signal is in its "do ...upto LAP" statement. Either it emits FROZEN\_TIME, and the button interpreter synchronously emits LAP, which should have killed the upto, thus preventing the emission of FROZEN\_TIME; or FROZEN\_TIME is not emitted, so neither is LAP, and FROZEN\_TIME should have been emitted.

The following example of a program without behavior is similar to the positive feedback obtained by plugging the output of an amplifier into its input:

```

signal S(combine integer with PLUS) in

emit S(0);

emit S(?S+1)

end

```

The integer value ?S conveyed by S should satisfy ?S = ?S+1!

#### 2.5.2 Multiple behavior

A slight modification of the previous example shows a second kind of paradox:

```

signal S in

present S then

emit S

else

nothing

end

end

```

Now, the local signal S must be present if and only if it is present! There are obviously two possible behaviors. Below is another program, which has infinitely many behaviors:

```

signal S(integer) in

emit S(?S)

end

```

The integer value conveyed by S is completely undetermined. ESTEREL considers such programs as erroneous, since determinism is one of its main goals.

Formally, all these problems come from the fact that the current event is a fixpoint of some function. Now, since this function is not always monotone, it can have 0, 1, or several fixpoints. ESTEREL semantics (in contrast with most semantics given to STATECHARTS [HPSS86, HGd88]) only give sense to programs that have one and only one fixpoint. We will see in §5.1 how this feature is statically checked by the ESTEREL compiler.

#### 2.5.3 Putting right the stopwatch

In order to avoid the causality loop in the stopwatch button interpreter, we only need to admit that the "frozen/running" time state of the stopwatch changes at the end of the reaction, when the signal LAP occurs. We have to replace, in the corresponding flip-flop, an interrupt by a withdrawal (cf. definitions, page 18):

```

% flip-flop "running-time/frozen-time"

loop % running-time state

await LAP;

trap T in

sustain FROZEN_TIME

||

await LAP; exit T

end

end

end.

```

Now, when LAP occurs, FROZEN\_TIME is emitted before exiting the "trap T" block.

# 2.6 Another example: the reflex game

# 2.6.1 Specifications

We consider a machine allowing a player to test his reflexes [Bou91]. The player controls the machine with three commands: putting a coin in a COIN slot to start the game, pressing a READY button to start a reflex measure, and pressing a STOP button to end a measure.

The machine reacts to these commands by operating the following devices: a numerical DISPLAY that shows reflex times, a GO lamp that signals the beginning of a measure, a GAME\_OVER lamp that signals the end of a game, a RED lamp that signals that the player has tried to cheat or has abandoned the game, and a BELL that rings when the player hits a wrong button.

When the machine is turned on, the DISPLAY shows 0, the GAME\_OVER lamp is on, the GO and RED lamps are off. The player then starts a game by inserting a COIN, which turns off the GAME\_OVER lamp. Each game

consists of a fixed NUMBER of reflex measures. A measure starts when the player presses the READY button; then, after a random amount of time, the GO lamp turns on and the player must press the STOP button as fast as he can. When he does so, the GO lamp turns off and the reflex time, measured in milliseconds, is displayed on the numerical DISPLAY. A new measure starts when the player presses READY again. When the cycle of NUMBER measures is completed, the average reflex time is displayed after a pause of PAUSE\_LENGTH milliseconds and the GAME\_OVER lamp is turned on.

There are five exception cases. Two of them are simple mistakes and make the BELL ring:

- the player presses STOP instead of READY to start a measure; or

- the player presses READY during a measure.

In the other three cases, the RED and GAME\_OVER lamps are turned on, the GO lamp is turned off, and the game ends:

- the player does not press the READY button within TIME\_LIMIT milliseconds when he is expected to (one assumes that the player has abandoned the game);

- the player does not press the STOP button within TIME\_LIMIT milliseconds when he is expected to (i.e., after the GO lamp turns on; this is also assumed to be an abandon);

- the player presses the STOP button after he has pressed the READY button but before the machine turns the GO lamp on, or at the same time that this happens (this is cheating!).

A last anomaly appears if the player inserts a COIN during a game. Then a new game is started at once.

#### 2.6.2 Interface

Three parameters of the machine are declared as integer constants: the NUMBER of measures and the delays PAUSE\_LENGTH and TIME\_LIMIT. They must be defined in the host language. An external function RANDOM is

used to determine the random delay at which the GO lamp turns on after the READY button is hit. The input signals are the millisecond time unit MS and the three user commands. As far as input relations are concerned, all input signals are assumed incompatible except MS and STOP: if the player presses STOP simultaneously with the occurrence of MS which terminates the random delay, then he must be considered as a cheater. To control a lamp (say GO), we introduce two output signals ON and OFF (hence GO\_ON and GO\_OFF). We also have output signals for the display and to ring the bell:

## 2.6.3 Computation of the average reflex time

We use a submodule to compute the average response time. This simple module emits AVERAGE\_VALUE whenever it receives an UPDATE\_AVERAGE signal with a new measure result:

```

module AVERAGE :

input UPDATE_AVERAGE(integer);

output AVERAGE_VALUE(integer);

var    MEASURE_NUMBER := 0 ,

TOTAL_TIME := 0 : integer in

every immediate UPDATE_AVERAGE do

TOTAL_TIME := TOTAL_TIME + ?UPDATE_AVERAGE;

MEASURE_NUMBER := MEASURE_NUMBER + 1;

emit AVERAGE_VALUE( TOTAL_TIME/MEASURE_NUMBER)

end

end

```

Notice the keyword immediate, which ensures that even an update occurring at the initial instant is handled.

#### 2.6.4 The program body

The body is made of two successive parts: some overall initializations and a main loop over a single game that is restarted whenever a coin is inserted. This main loop is simply controlled by an "every COIN" statement.

Within a single game, we declare an ERROR trap to handle the cheating tentatives and an END\_GAME trap to handle the normal game termination. Whenever the loop is entered, an instance of the module AVERAGE is put in parallel with the main process, with which it communicates by means of the two local signals UPDATE\_AVERAGE and AVERAGE\_VALUE. The general structure of the program is thus the following:

Overall initializations consist in turning off the GO and RED lamps, turning on the GAME\_OVER lamp, and initializing the display to 0. The game initializations only differ by turning off the GAME\_OVER lamp.

The main process of a game consists in performing NUMBER measures, and then in displaying the average time:

```

repeat NUMBER times

<measure>

end;

await PAUSE_TIME MS;

emit DISPLAY(?AVERAGE_VALUE);

exit END_GAME

```

Each measure consists of three steps:

1. Wait for the READY signal within a time limit of TIME\_LIMIT. In case of timeout, an error is detected. While waiting, any occurrence of STOP rings the bell (this is the short example given in §2.4.1):

```

% step (1)

do

do

every STOP do emit RING_BELL end

upto READY

watching TIME_LIMIT MS

timeout exit ERROR end

```

2. Wait for a random delay, and after this delay, switch on the GO lamp. While waiting, any hit on the STOP button causes an error. Since an error must be detected even when the STOP button is hit simultaneously with the end of the random delay, the interrupt by STOP is given priority over the random delay. While waiting, any hit on the READY button rings the bell:

3. Wait for the STOP signal, counting milliseconds, within a TIME\_LIMIT delay. In case of timeout, an error is detected. While waiting, any hit on the READY button rings the bell. When the STOP

signal occurs, the GO lamp is turned off and the counted measure is displayed:

```

% step (3)

do

var TIME := 0 : integer in

do

every MS do TIME := TIME+1 end

||

every READY do emit RING_BELL end

upto STOP;

emit DISPLAY(TIME);

emit UPDATE_AVERAGE(TIME);

emit GO_OFF

end

watching TIME_LIMIT MS

timeout exit ERROR end;

```

If an error occurs, the RED lamp is turned on, and the GO lamp is turned off. At the end of a game, the GAME\_OVER lamp is turned on. The whole program is given in Figure 2.1.

```

{\tt module} \ \ REFLEX\_GAME \ :

constant NUMBER, PAUSE_LENGTH, TIME_LIMIT : integer;

function RANDOM() : integer;

input MS, COIN, READY, STOP;

relation MS # COIN # READY, COIN # STOP, READY # STOP;

\verb"output" GO\_ON, GO\_OFF, GAME\_OVER\_ON, GAME\_OVER\_OFF,

RED_ON, RED_OFF, DISPLAY(integer), RING_BELL;

% overall initializations